采用CPLD來替代微處理器的6種方法

看門狗定時器

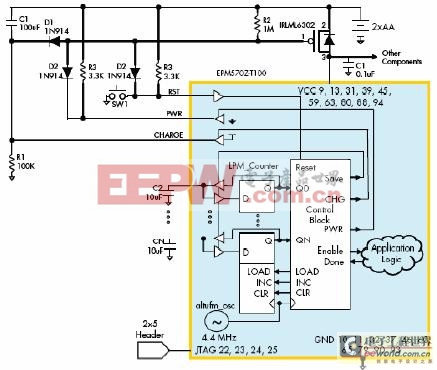

很多系統管理應用需要采用定時器。設計人員可能會吃驚地發現CPLD可以用于實現通常由微控制器完成的定時器功能。利用幾個分立電容、電阻、二極管和金屬氧化物半導體場效應晶體管(MOSFET),設計一個簡單但是有效的電阻電容(RC)定時器電路,周期性的對CPLD上電。在圖4的實例電路中,設置RC值來建立一個10秒定時器。可以利用三個外部電容(C1、C2和C3)來擴展這一基本定時器,三個電容被用于建立一個簡單的非易失二進制計數器。這樣,在MAX IIZ EPM240Z CPLD中利用19%的邏輯就可以完全實現從10秒到80秒的間隔周期(2)。

圖4. 為MAX IIZ CPLD開發基于定時器的上電電路

CPLD和微控制器結合使用的實例

CPLD并不總是和微控制器相競爭。在以下幾個例子中,CPLD是微控制器優異的輔助器件。

GPIO引腳擴展

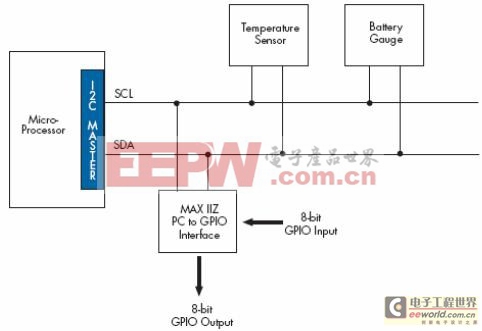

在常見的通用I/O(GPIO)引腳擴展應用中,設計人員把低成本小型微控制器的可編程功能和CPLD的通用IO資源結合起來使用。CPLD構建一組內部寄存器,微控制器通過I2C或者SPI等串口來訪問這些寄存器(圖5),使微控制器能夠使用現有的I/O資源來擴展其I/O總數量。利用擴展I/O,設計人員還可以使用CPLD進行電平轉換,從而提高了CPLD的實用性(3)。

圖5. GPIO引腳擴展

端口管理

便攜式應用設計人員經常需要連接具有不同I/O接口的器件。這一功能被稱為橋接,因為采用CPLD來構成不同接口之間的“橋”。這一節介紹三個這樣的例子:

- 串行至串行 - I2C至SPI

- 串行至并行 – SPI器件(串行)至主處理器(并行)

- 并行至并行 - 主處理器至CF+

在每一例子中,有幾個原因表明為什么CPLD是優于微控制器的選擇。一個原因是微控制器不能有效地提供需要的I/O數量。采用微控制器不一定能滿足接口需要的性能。此外,在微控制器中實現這些功能要比在CPLD硬件中復雜得多。

評論