一種出租車計價器的FPGA設計方案及應用

2.2 三位BCD碼加法器

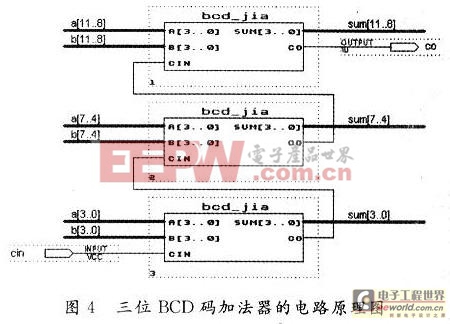

系統中用到了三位BCD碼加法器,可以實現三位十進制數的加法運算。加法器輸出的結果就是乘客應付的費用,這里同樣以前兩位為整數,第三位為小數,也就是最大能顯示99.9元。三位BCD碼加法器由三個一位BCD碼加法器級聯而成。

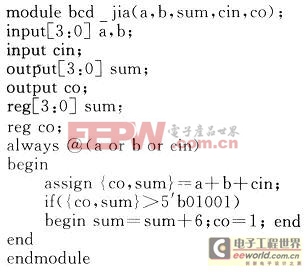

一位BCD碼由四位二進制數組成,四位二進制數的加法運算會產生大于9的數字,必須進行適當的調整才會產生正確的結果。一位BCD碼加法器的Verilog HDL源程序如下:

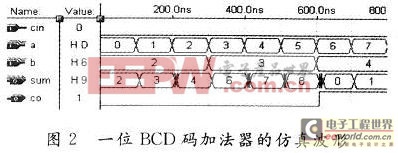

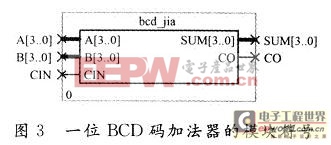

一位BCD碼加法器模塊的仿真波形和生成的模塊符號如圖2和圖3所示。

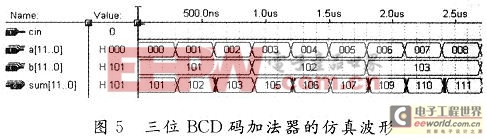

本模塊中A和B為輸入的一位BCD碼,CIN為低位來的進位信號,CO是本片向高位產生的進位輸出信號,SUM是兩個數相加的和。三位BCD碼加法器由三個本模塊級聯而成,其電路原理圖和仿真波形如圖4和圖5所示。

評論