基于FPGA的二次群分接器的結構分析及實現

4.基群信號提取

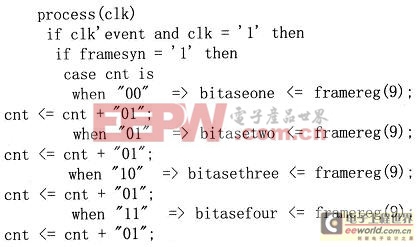

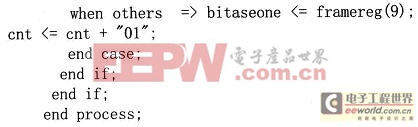

一個二次群信號復接了四個基群信號,基群信號提取是在二次群幀同步的狀態下把二次群信號按一分四的規則進行串并轉化。因為二次的復接是按bit復接,所以二次群一幀中第一位為第一個群的第一位,二次群一幀中第二位為第二個群的第一位,以此類推。VHDL語言代碼實現如下程序段:

5.去除插入碼及負碼速調整

去除插入碼及負碼速調整是二次群的關鍵部分,首先要去除幀頭插入的F1、F2和F3;接著去除C1、C25DC3;最后根據C1、C2和C3值來判斷第161位V否為插入碼,如果C1C2C3為:"1 11",則V是插入碼應去除,如果C1C2C3為:"000",則V是基群的信碼,不應去除。把去除了插入碼的信號輸入到一個FIFO,用經過負碼速調整過的2.048MHz時鐘讀出輸出基群信號如圖3所示。

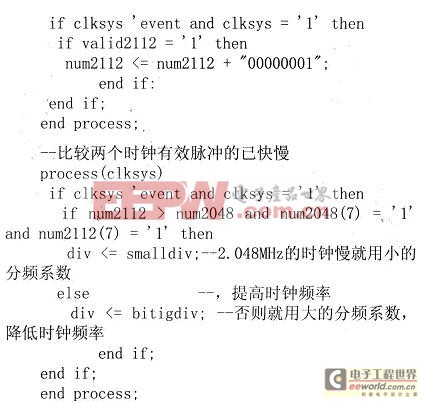

由于寫到FIF0的時鐘是不均勻的,不利于后端處理,所以必須做負碼速調整,即把2.112MHz速率調整到2.048MHz速率。FPGA實現的原理是根據2.112MHz速率和2.048MHz速率的有效信碼個數是一樣多的,可以根據它們的個數進行調整。如果根據2.048MHz速率輸出的信碼少了則稍微提高2.048MH z時鐘的頻率,如果根據2.048MHz速率輸出的信碼多了則稍微降低2.048MHz時鐘的頻率。

VHDL語言代碼實現如下程序段:一根據div的值動態調整clk2048的頻率,實現負碼速調整。

6.結論

本文對二次群的分接處理,提出了一種基于FPGA的方案,介紹了二次群的幀結構,給出了幀頭捕獲、幀丟失告警、負碼速調整等VHDL語言的關鍵程序。在QUARTUSII軟件中編譯完成,資源僅占用三十多個LE,給二次群設備的設計提供了一種參考,具有很高的應用價值。

評論