利用低成本FPGA設計下一代游戲控制臺

基于平臺的游戲控制臺設計考慮因素

FPGA可以幫助系統設計者盡可能地節約成本并提供最大的靈活性,這是由基于平臺方法通過提供以下設計方針來實現的。

需求和模型可隨著區域而變化:針對多個標準和格式提供可編程支持能加快產品上市時間;低成本和可靠的設計:集成全部的系統I/O接口、控制邏輯和調試功能,以支持連接至HDD和內部存儲器的ASIC/ASSP芯片組的橋接功能,定制的用戶接口邏輯可降低在新產品中的風險;在最終測試期間和現場的安全編程能夠實現對多種標準的支持、協處理算法的增量升級以及易于對新功能進行測試。

帶有嵌入式DSP解決方案的FPGA

在選擇面向平臺的可編程器件時,通常需考慮三種電路要求:面向協處理功能的嵌入式DSP的功能和性能、查找表(LUT)以及RAM塊(EBR),這種協處理功能利用并行方法,針對具體應用以最優成本對功能和性能進行裁剪。低電壓差分信號(LVDS)和串行解串器(SERDES)可支持高速芯片至芯片接口,如HyperTransport、PCI Express或串行RapidIO。能夠安全地保護知識產權。

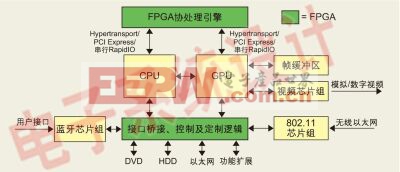

圖2顯示了一個滿足這些要求的FPGA解決方案。FPGA被連接到主CPU、圖像處理芯片、用戶接口和諸如無線以太網的其它關鍵ASSP。FPGA模塊執行協處理功能和硬件加速,并具有實現未來功能所必需的定制邏輯,這些功能是針對用戶接口或控制臺的其它部分。

圖2:可重構FPGA能支持多個I/O標準、高速接口以及針對硬件加速的協處理算法。

DSP協處理和硬件加速

盡管低成本FPGA通常工作在小于300MHz的系統時鐘頻率下,但通過并行地執行串行功能仍然可實現很高的DSP吞吐量(63,000MMAC)。例如,某個應用要求具有100MS/s采樣率的32抽頭FIR濾波器,那么需要帶有4個乘法器的通用DSP處理器以800MHz計算乘累加。具有32個乘法器的FPGA能夠在100MHz實現相同的濾波器。

與乘法器一樣,能夠靈活地利用FPGA的并行特性有益于存儲器訪問。片上分布式存儲器可用來構建小容量高性能臨時存儲器,而片上嵌入式存儲塊可用來構建大容量高性能存儲器。DDR DRAM等片外存儲器則可以提供大容量、高性能存儲器。

評論