一種基于FPGA實現的全數字鎖相環

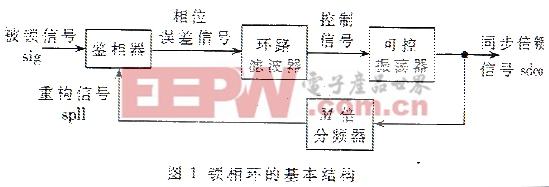

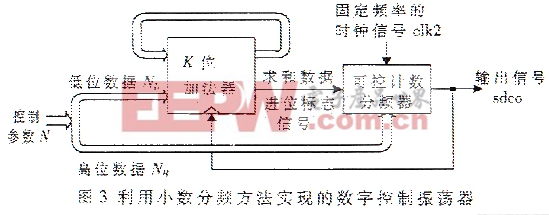

1 實現結構 1.1 鑒相器 作為一個完整的數字鎖相環系統,鑒相器的選擇對鎖相性能影響很大。傳統的具有雙觸發結構的鑒相器需要依靠信號在器件和線路中的延時來工作,而且在電路中會產生毛刺脈沖,不便于在FPGA中實現。為此,本文采用圖2所示的基于狀態轉移時序邏輯的信號鑒相器。被鎖脈沖信號sig和本地重構信號spll輸入該鑒相器后,首先在時鐘信號clk1的控制下借助鎖存器和上升沿判斷邏輯分別獲得上升沿判斷脈沖信號e1和e2。然后e1和e2經過具有鎖存反饋的鑒相狀態轉移邏輯產生兩個相位誤差信號up和down。相位誤差信號up和down利用其負脈沖信號的出現反映兩個輸入脈沖信號sig和spll的頻率高低。而且負脈沖的寬度可以反映sig和spll之間的相位差。該鑒相器易于在可編程邏輯器件中實現,避免了毛刺信號的產生。圖21.2 為了提高輸出信號的頻率控制精度,減小鎖相環輸出信號的相位抖動,選擇利用小數分頻方法實現的數字控制振蕩器。如果分頻控制參數N具有k位的小數部分,則其實現結構如圖3所示。 1.3 利用比例積分方法實現的鎖相控制 本文中鎖相環采用了比例積分控制邏輯替代傳統鎖相系統中的環路濾波,用以產生可控振蕩器的輸入控制參數N。該方法的實現原理框圖如圖4所示。 在利用比例積分方法實現鎖相控制的原理框圖中,鑒相器產生的相位誤差信號up他down的負電平有效信號分別被工作時鐘clk3調成為一組狀計數和增計數脈沖序列。在比例控制通路中,增減脈沖首先要經過比例脈沖分頻器分頻(分頻倍數為PG),得到比例增脈沖和比例減脈沖。然后,比例增減計數器對該脈沖信號進行增1或減1計數。比例增減計婁和器在被鎖信號sig清零之前所獲得的計數值將被存儲到數據鎖存器中,從而獲得比例控制參數Np。在積分控制通路中,增減脈沖也要先經過分頻倍數為IG的積分脈沖分頻器分頻,得到積分增減脈沖信號。然后,積分增減計數器對該脈沖計數,計數的輸出結果作為積分控制參數NI。比例如積分通路各自產生的控制參數Np和N1最后被加在一起,得到鎖相環的振蕩器控制參數N。

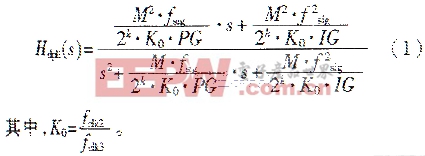

1 實現結構 1.1 鑒相器 作為一個完整的數字鎖相環系統,鑒相器的選擇對鎖相性能影響很大。傳統的具有雙觸發結構的鑒相器需要依靠信號在器件和線路中的延時來工作,而且在電路中會產生毛刺脈沖,不便于在FPGA中實現。為此,本文采用圖2所示的基于狀態轉移時序邏輯的信號鑒相器。被鎖脈沖信號sig和本地重構信號spll輸入該鑒相器后,首先在時鐘信號clk1的控制下借助鎖存器和上升沿判斷邏輯分別獲得上升沿判斷脈沖信號e1和e2。然后e1和e2經過具有鎖存反饋的鑒相狀態轉移邏輯產生兩個相位誤差信號up和down。相位誤差信號up和down利用其負脈沖信號的出現反映兩個輸入脈沖信號sig和spll的頻率高低。而且負脈沖的寬度可以反映sig和spll之間的相位差。該鑒相器易于在可編程邏輯器件中實現,避免了毛刺信號的產生。圖21.2 為了提高輸出信號的頻率控制精度,減小鎖相環輸出信號的相位抖動,選擇利用小數分頻方法實現的數字控制振蕩器。如果分頻控制參數N具有k位的小數部分,則其實現結構如圖3所示。 1.3 利用比例積分方法實現的鎖相控制 本文中鎖相環采用了比例積分控制邏輯替代傳統鎖相系統中的環路濾波,用以產生可控振蕩器的輸入控制參數N。該方法的實現原理框圖如圖4所示。 在利用比例積分方法實現鎖相控制的原理框圖中,鑒相器產生的相位誤差信號up他down的負電平有效信號分別被工作時鐘clk3調成為一組狀計數和增計數脈沖序列。在比例控制通路中,增減脈沖首先要經過比例脈沖分頻器分頻(分頻倍數為PG),得到比例增脈沖和比例減脈沖。然后,比例增減計數器對該脈沖信號進行增1或減1計數。比例增減計婁和器在被鎖信號sig清零之前所獲得的計數值將被存儲到數據鎖存器中,從而獲得比例控制參數Np。在積分控制通路中,增減脈沖也要先經過分頻倍數為IG的積分脈沖分頻器分頻,得到積分增減脈沖信號。然后,積分增減計數器對該脈沖計數,計數的輸出結果作為積分控制參數NI。比例如積分通路各自產生的控制參數Np和N1最后被加在一起,得到鎖相環的振蕩器控制參數N。 2 參數設計 2.1 數學模型 如果設被鎖信號sig的頻率是fsig,圖3中時鐘信號clk2的頻率為fclk2,圖4中調制處理所用的時鐘信號clk3的頻率為felk3,則鎖相環在被鎖信號頻率附近的局部動態數學模型的傳遞函數為:

2 參數設計 2.1 數學模型 如果設被鎖信號sig的頻率是fsig,圖3中時鐘信號clk2的頻率為fclk2,圖4中調制處理所用的時鐘信號clk3的頻率為felk3,則鎖相環在被鎖信號頻率附近的局部動態數學模型的傳遞函數為:  Hdpll(s)是一個二階系統的傳遞函數。而且,該二階系統的自然頻率ωn為:

Hdpll(s)是一個二階系統的傳遞函數。而且,該二階系統的自然頻率ωn為:  該系統的阻尼系數ξ為:

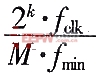

該系統的阻尼系數ξ為:  由式(2)和式(3)可知,如果在鎖相系統的設計中確定了參數K0、M、k、IG和PG則自然頻率ωn將與被鎖信號頻率fsig成玻比,而阻尼系數ξ具有確定的數值,即ξ與被鎖信號狀態無關。一方面,依據自動控制理論,二階系統的阻尼系數ξ決定了系統達到穩定的響應形式。當阻尼系數ξ固定時,自然頻率決定了系統達到穩定的速度。由于本鎖相系統在不同的被鎖頻點具有相同的阻尼系數,所以在被鎖頻點的局部范圍內,鎖相跟蹤過程將以相同的形式達到穩定。另一方面,由于自然頻率ωn與被鎖相信號頻率fsig成正比,則說明本鎖相環從在被鎖信號頻率附近發出鎖定被信號的時刻開始,到鎖相趨于穩定所需要的時間與被鎖信號的周期成正比。所以可以得出結論:當被鎖信號的頻率范圍較寬時,本鎖相環系統在不同的被鎖頻點的局部范圍內部都具有一致的鎖相速度和穩定性。這一特性要優于已有的數字鎖相系統。圖42.2 參數設計 依據具體的應用需要,可以按照如下步驟設計該鎖相環: (1)確定被鎖信號的頻率范圍(fmin,fmax)和鎖相同步的分頻倍數M,且fmax<100%26;#183;fmin; (2)圖2、圖3和圖4中的時鐘信號clk1、clk2和clk3可以取同一時鐘源clk且有K0=1,該時鐘頻率fclk還應至少比M%26;#215;fmax高一個數量級; (3)選擇小數分頻位數k,一般k應該滿足:2k

由式(2)和式(3)可知,如果在鎖相系統的設計中確定了參數K0、M、k、IG和PG則自然頻率ωn將與被鎖信號頻率fsig成玻比,而阻尼系數ξ具有確定的數值,即ξ與被鎖信號狀態無關。一方面,依據自動控制理論,二階系統的阻尼系數ξ決定了系統達到穩定的響應形式。當阻尼系數ξ固定時,自然頻率決定了系統達到穩定的速度。由于本鎖相系統在不同的被鎖頻點具有相同的阻尼系數,所以在被鎖頻點的局部范圍內,鎖相跟蹤過程將以相同的形式達到穩定。另一方面,由于自然頻率ωn與被鎖相信號頻率fsig成正比,則說明本鎖相環從在被鎖信號頻率附近發出鎖定被信號的時刻開始,到鎖相趨于穩定所需要的時間與被鎖信號的周期成正比。所以可以得出結論:當被鎖信號的頻率范圍較寬時,本鎖相環系統在不同的被鎖頻點的局部范圍內部都具有一致的鎖相速度和穩定性。這一特性要優于已有的數字鎖相系統。圖42.2 參數設計 依據具體的應用需要,可以按照如下步驟設計該鎖相環: (1)確定被鎖信號的頻率范圍(fmin,fmax)和鎖相同步的分頻倍數M,且fmax<100%26;#183;fmin; (2)圖2、圖3和圖4中的時鐘信號clk1、clk2和clk3可以取同一時鐘源clk且有K0=1,該時鐘頻率fclk還應至少比M%26;#215;fmax高一個數量級; (3)選擇小數分頻位數k,一般k應該滿足:2k 的正整數,取積分增減計數的下限閾值Nimin為略小于

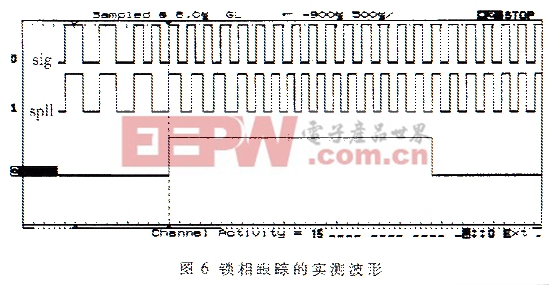

的正整數,取積分增減計數的下限閾值Nimin為略小于 的正整數;比例增減計數的上限閾值Npmax取小于Nimin的正整數,而其下限閾值Npmin可以等于-Npmax。 3 設計實例 基于上述的鎖相環結構和設計方法,本文采用MAX+PLUS II軟件設計了一個鎖相環實例。具體的參數設計如下:被鎖相信號的輸入頻率范圍為850Hz~12kHz;鎖相環中的分頻倍數M=40;鑒相控制時鐘clk1、數字控制振蕩器的時鐘clk2和比例積分控制中的工作時鐘clk3采用頻率為8MHz的同一時鐘信號;數字控制振蕩器的二進制小數分頻控制位數k=4;積分分頻的倍數IG=25,比例分頻的倍數PG=5,即阻尼系數ξ=0.79,自然頻率ωn=0.316fsig,理論估計的局部穩定時間約為14個被鎖相號周期;積分增減計數的上限閾值取Nimax=3840,下限閾值取Mimin=256;比例增減計數的上限閾值取Ppmax=255,下限閾值取Npmin=255。圖5基于MAX+PLUS II軟件對上述鎖相環邏輯電路的仿真波形如圖5所示。在圖5中,clk1是時鐘信號,sig的輸入的被鎖信號,spll是本地重構信號,N是可控振蕩器的控制參數,其數據為16進制。當圖5中被鎖信號頻率突然由高變低時,鎖相環在20個被鎖信號周期內基本可以跟蹤上輸入信號。 本文基于型號為EP1K100QC208的FPGA設計了實驗電路,該電路的時鐘頻率8MHz。在所設計的鎖相環邏輯電路中,為了便于鑒視鎖相環的工作狀況,增加了一個鎖相監視的判斷信號LOCK。當鎖相控制中的比例控制參數NP超過了設定閾值時,則LOCK信號有效。采用惠普54620A邏輯分析儀,將LOCK信號作為觸發源,所錄制的被鎖信號sig和本地重構信號spll波形如圖6所示。在圖6所示,被鎖相信號sig的頻率由3kHz階路到6kHz,鎖相跟蹤過程在20個被鎖信號周期后達到了鎖相同步。

的正整數;比例增減計數的上限閾值Npmax取小于Nimin的正整數,而其下限閾值Npmin可以等于-Npmax。 3 設計實例 基于上述的鎖相環結構和設計方法,本文采用MAX+PLUS II軟件設計了一個鎖相環實例。具體的參數設計如下:被鎖相信號的輸入頻率范圍為850Hz~12kHz;鎖相環中的分頻倍數M=40;鑒相控制時鐘clk1、數字控制振蕩器的時鐘clk2和比例積分控制中的工作時鐘clk3采用頻率為8MHz的同一時鐘信號;數字控制振蕩器的二進制小數分頻控制位數k=4;積分分頻的倍數IG=25,比例分頻的倍數PG=5,即阻尼系數ξ=0.79,自然頻率ωn=0.316fsig,理論估計的局部穩定時間約為14個被鎖相號周期;積分增減計數的上限閾值取Nimax=3840,下限閾值取Mimin=256;比例增減計數的上限閾值取Ppmax=255,下限閾值取Npmin=255。圖5基于MAX+PLUS II軟件對上述鎖相環邏輯電路的仿真波形如圖5所示。在圖5中,clk1是時鐘信號,sig的輸入的被鎖信號,spll是本地重構信號,N是可控振蕩器的控制參數,其數據為16進制。當圖5中被鎖信號頻率突然由高變低時,鎖相環在20個被鎖信號周期內基本可以跟蹤上輸入信號。 本文基于型號為EP1K100QC208的FPGA設計了實驗電路,該電路的時鐘頻率8MHz。在所設計的鎖相環邏輯電路中,為了便于鑒視鎖相環的工作狀況,增加了一個鎖相監視的判斷信號LOCK。當鎖相控制中的比例控制參數NP超過了設定閾值時,則LOCK信號有效。采用惠普54620A邏輯分析儀,將LOCK信號作為觸發源,所錄制的被鎖信號sig和本地重構信號spll波形如圖6所示。在圖6所示,被鎖相信號sig的頻率由3kHz階路到6kHz,鎖相跟蹤過程在20個被鎖信號周期后達到了鎖相同步。 本文基于FPGA實現了一種新型的全數字鎖相環。在性能方面,該鎖相環具有很寬的鎖相范圍、快速的響應能力和良好的穩定性。在應用方面,該鎖相環具有易于實現的邏輯結構,并且能夠依據鎖相速度和穩定性要求選取設計參數。本文給出了具體的參數設計步驟,并具體介紹了一個設計實例。通過MAX+PLUS II軟件的仿真和基于FPGA的實際測量,證明了本文提供的設計方法的正確性和該鎖相環的良好性能。該鎖相環可以應用于基于CPLD或FPGA的電力系統控制裝置中,并為同步控制提供快速可靠的基準信號。

本文基于FPGA實現了一種新型的全數字鎖相環。在性能方面,該鎖相環具有很寬的鎖相范圍、快速的響應能力和良好的穩定性。在應用方面,該鎖相環具有易于實現的邏輯結構,并且能夠依據鎖相速度和穩定性要求選取設計參數。本文給出了具體的參數設計步驟,并具體介紹了一個設計實例。通過MAX+PLUS II軟件的仿真和基于FPGA的實際測量,證明了本文提供的設計方法的正確性和該鎖相環的良好性能。該鎖相環可以應用于基于CPLD或FPGA的電力系統控制裝置中,并為同步控制提供快速可靠的基準信號。

評論