基于Python 定點平方根的FPGA實現

2.4 綜合結果

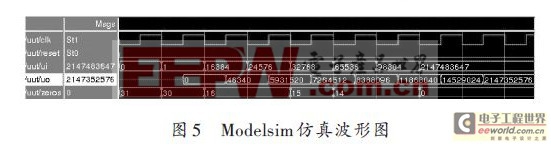

在上面仿真校驗符合設計要求后,將Python自動轉換為Verilog描述,采用Quartus編譯綜合,并使用Model-sim仿真的波形如圖5所示,與圖3的Python環境下仿真波形相似,由此可見采用Python的軟硬件協同設計方法能有效地進行FPGA 設計。綜合后FPGA 資源使用情況:LE共1 506個,寄存器64個,嵌入式9位硬件乘法器10個。

3 結論

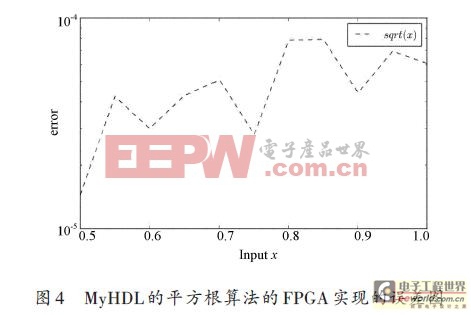

本文采用基于Python的擴展包MyHDL的軟硬件協同設計方法,在FPGA 上完成了定點平方根算法,設計仿真過程僅使用Python語言,所以仿真校驗和傳統的設計方法相比效率更高,仿真速度也更快,另外此方法還可以方便,有效地將一個軟件算法快速地轉換為其相應的硬件實現,從而完成軟硬件系統協同設計。

現代系統的算法越來越復雜,傳統的軟硬件設計方法越來越不適應市場對設計的要求,采用Python進行系統設計,仿真和校驗的速度會大大地提高,也能夠自動將算法轉換為對應的硬件實現,所以采用Python來進行軟硬件協同設計的產品能更快地進入市場,并且隨著設計復雜性的進一步增強和這種設計方法本身的發展和完善,基于Python的軟硬件協同設計方法將會有更加廣闊的應用前景。

評論