基于FPGA的視頻圖像分割技術設計與應用

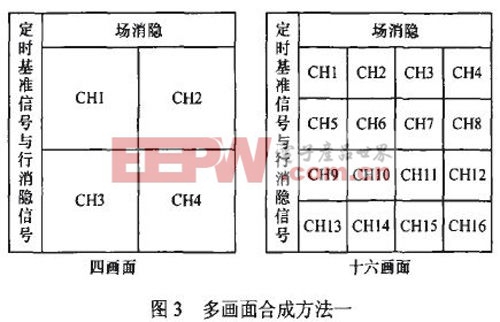

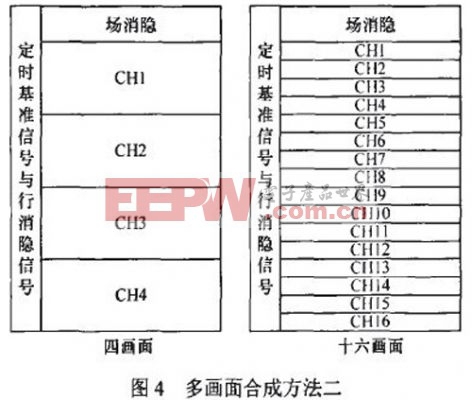

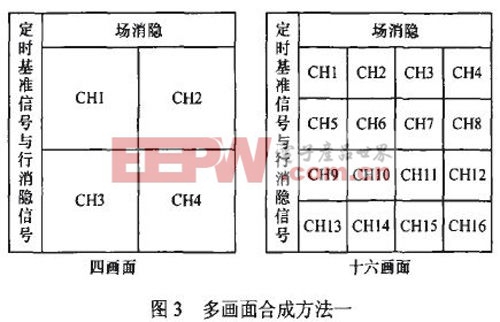

通過實驗得到另一個結論:在DSP內部是用DMA來搬運視頻數據到顯示bu仃er的相應位置。對于數據量相對較大的“數據塊”來說,DMA所耗費的系統性能是非常接近的。由此,筆者設計出第2種換面合成方式,如圖4所示。這樣做可以簡化邏輯設計,節約FPGA資源,提高項目開發速度。

2 系統設計

2.1 硬件設計部分

圖5是FPGA相關部分硬件框圖,可以看到,16路視頻數據由4片TW2815芯片輸入到FPGA,經過分割合成處理后送入DSP。由于視頻數據速度高、數據量大,所以采用兩片DDR SDRAM進行緩存。主時鐘為133 MHz,配置電路采用從串和JTAG模式,前者用于系統運行時由MCU進行配置,后者用于系統調試。FPGA芯片選用Xilinx公司Spaaen3ADSP系列

XC3SD3400A芯片。系統由ATX電源供電,內部各電平由電源芯片產生。內存為兩片HY5DU561622ETP型DDR SDRAM。

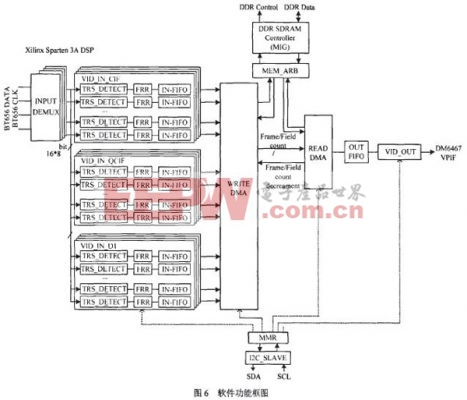

2.2 軟件功能架構

圖6為軟件設計功能框圖,它由多個功能模塊組成。各模塊功能如下:

1,INPUT DEMUX:接收視頻數據,根據視頻解碼芯片的工作模式將信號分解成ITU-RBT.656數據送入下級模塊。

2,VII)IN:檢測SAV、EAV信號,提取有效視頻數據(DI、CIF、QCIF),然后放入FIFO中暫存。

3,WRITE DMA:按照設計中對內存的劃分,將不同通道的有效數據寫入設定的內存空間。

4,READ DMA:按照一定的格式讀取內存空間中的數據。

5,MEM ARB:仲裁對內存的讀寫操作,協調讀寫模塊工作。

6,DDR SDRAM Controller:用Xilinx內存接口生成器(MIG)生成,實現FPGA與DDR接口

7,VID OUT:在輸出視頻數據中添加通道號等輔助信息,便于DSP識別。

8,12C_SLAVE:模擬12c從模塊工作方式,外部MCU通過該接口對內部寄存器進行配置,以實現不同功能。

整個系統基于同步邏輯設計,使用Verilog HDL語言進行代碼編寫,仿真使用ModelSim,圖7是其中典型一次寫突發過程模塊的仿真波形。

評論