用于CMOS圖像傳感器的流水線ADC設計及其成像驗證

另外,由于余量放大器有限的帶寬,因此對輸入電壓響應需要經過一定的時間才能趨于穩定。在采樣頻率為f的ADC中,要求信號在二分之一的時鐘周期內達到所需的精度(即誤差小于1/2LSB),即有:

![]()

式中GBW為單位增益帶寬,N為ADC分辨率,β為反饋系數,f為采樣頻率。

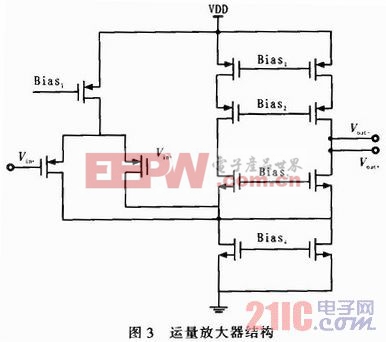

對于本文的ADC設計有:N=12,β=1/2,f=10 MHz,因此由公式(1)和公式(2)可得,用于本文第一級MDAC的余量放大器應滿足:開環增益需大于84 dB,單位增益帶寬需大于58 MHz。綜合考慮到輸入信號擺幅、流片工藝和功耗等要求,本文的余量放大器采用了折疊共源共柵的運放結構,仿真結果表示,該結構可滿足設計要求。

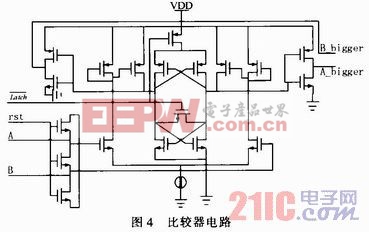

2.2 比較器設計

流水線ADC由于采用了校正電路,對比較器失調電壓的要求放寬了。對于1.5 bit每級的電路,設參考電壓為1 V,則它的失調電壓放寬為125 mV。本ADC中從第1級到第10級電路都采用了動態比較器,因為其失調電壓小于可校正的最大失調電壓,同時它具有較快的速度和較低的功耗。該電路的原理圖如圖4所示,它包括一個由rst信號控制的快速復位電路、信號輸入的預防大電路、鎖存比較器以及輸出反相器組成。

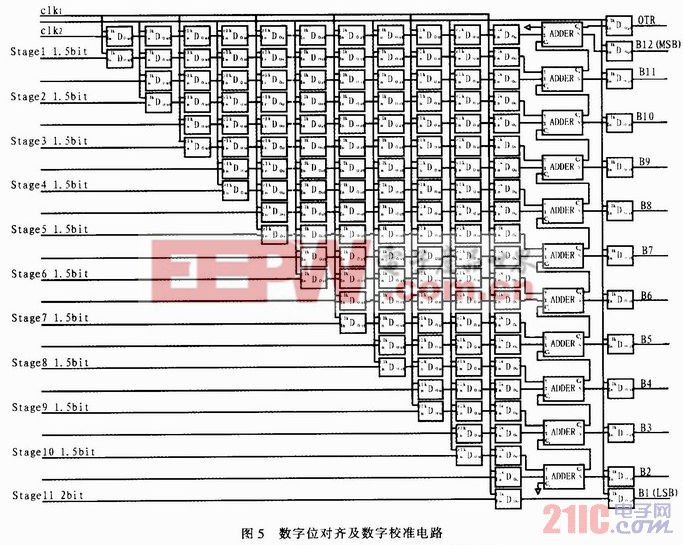

2.3 數字位時間對齊及數字校準電路設計

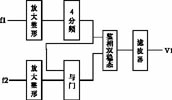

由于流水線ADC每級電路產生數字代碼的時間不同,因此,在進行數字校正之前,必須先對其進行延遲,所以在數字校正電路之前必須要有數字延遲電路。完整的輸出數字時間對齊及數字校正電路如圖5所示,其中圖的左邊為數字位時間對齊電路,圖的右邊為數字校準電路。

2.4 時鐘控制電路設計

流水線ADC對于時序要求比較高,為了確保流水線ADC正常工作,要求前后兩級不同時工作在采樣狀態和保持狀態,至少需要一對兩相不交疊時鐘。文中設計的時鐘信號電路如圖6所示。相比一般的采用器件延時來設計時鐘控制電路,本文采用了在電路引入電容的方式來確定時鐘延時,盡管這樣做會在版圖上多占用了一些面積,但是其好處是設計的兩相不交疊時鐘非常穩定,時鐘可以根據電容值選取的大小而更為合理的錯開。

評論