利用FPGA解決TMS320C54K/SDRAM的接口問題

|

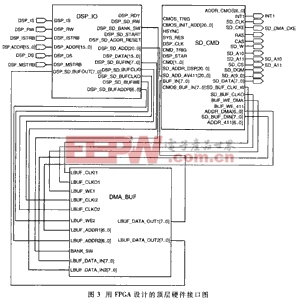

圖中主要有三個模塊:DSP-IO、DMA_BUF和SD-CMD。其中DSP-IO是DSP端的接口,用來解碼TMS320C54x發送的SDRAM地址和命令。DMA_BUF代表緩沖區B0、B1。SD_CMD模塊用來產生SDRAM訪問所需的各種信號。

DSP_IO模塊又包括IO_DMA、DSP_BUF和DSP_

READ。IO_DMA產生SDRAM的命令信號即圖3中的DSP_RDY、DSP_SD_RW、DSP_SD_BANK_SW、DSP_SD_

ADDR20..0、DSP_SD_ADDR_RESET、DSP_SD_START。

DSP_BUF產生訪問B0、B1的地址、數據和控制信號,圖3中指DSP_SD_BUFCLKI、DSP_SD_BUFCLKO、DSP_SD_

BUFWE、DSP_SD_BUFADDR6..0、DSP_SD_BUFIN7..0。DSP-READ子模塊用來控制DSP的讀寫方向。

DMA_BUF分為B0、B1兩個緩沖區,用來進行數據傳送每個緩沖區的輸入輸出信號包括CLKI、CLKO、WE、ADDR6-0、DATA_IN7-0、DATA_OUT7-0。

BANK_SW是一個開關信號用于DSP和SDRAM對B0、B1的切換訪問。

SD_CMD模塊包括刷新、讀、寫功能。當DSP芯片發出SDRAM讀命令時,128字節的數據從SDRAM中讀出來并被存儲到B0或B1中,當DSP發出寫命令之時,128字節的數據傳到B0或B1之中并被最終寫到SDRAM中。

4 軟件設計

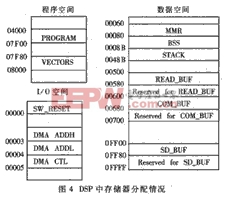

TMS626812A SDRAM有兩兆字節的存儲容量。所以DSP用兩個I/O地址向FPGA傳送訪問SDRAM的高低地址。此文中該兩個I/O地址對應于圖4中的03hDMA_ADDH和04hDMA_ADDL。另外,還有一個I/O地址圖4中的05h用來向FPGA傳送命令產生SDRAM訪問的信號。

DSP向SDRAM寫數據時的操作步驟如下:

|

1數據先被寫到B0或B1。

2SDRAM的訪問地址經由DSP的I/O地址DMA_ADDH和DMA_ADDL發送到FPGA中。

3DSP向FPGA發出一個命令(I/O地址為DMA_CTL)產生控制信號,使SDRAM從B0或B1中讀取數值。

DSP從SDRAM讀數據的操作步驟如下:

1DSP傳送訪問SDRAM的地址。

2DSP經由FPGA傳送一個命令,使得數據從SDRAM中讀到FPGA中。

3DSP從B0或B1中讀得數據。

圖4為DSP中與數據傳送相關的各類存儲器的分配情況。

具體設計時,應參考相關資料進行補充。不同的DSP與不同類型的SDRAM接口時,會有細微的區別,電路設計完畢后要進行認真而多方面的測試。

參考文獻

1 Application Report Spra531. Texas Instruments Incorporated

1999

2 王年旭.DSP基礎與應用系統設計.北京北京航空航天大

學出版社 2001

3 TMS626812A Synchronous Dynamic Random-Access Memo-

ries Data Sheet. Texas Instruments Incorporated1998

評論