電控噴油霧化檢測的DSP和FPGA通信模塊設計

0517.hex中的部分內容如下:

:04000000C000002AD2

:040001000000004487

:040002000000006496

:040003000000008871

:04000400000C008048

:04000500000000D91E

:040006000000102F3

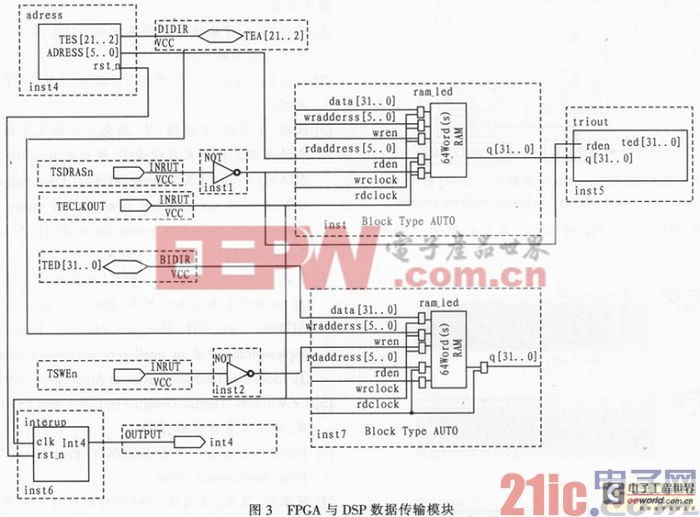

在QuartusII中用原理圖的形式創建FPGA與DSP數據傳輸模塊,如圖3所示。本文引用地址:http://cqxgywz.com/article/241674.htm

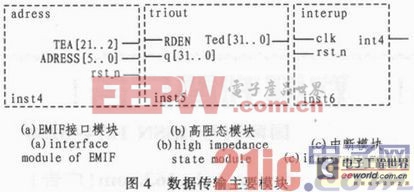

主要的功能模塊:1)EMIF接口模塊,如圖4(a)所示,該功能模塊為DSP與FPGA中的雙口RAM進行數據傳輸提供地址和數據總線。2)高阻態功能模塊如圖4(b)所示,該模塊的主要功能是防止總線沖突。3)中斷功能模塊如圖4(c)所示,該功能模塊為時鐘中斷,負責雙口RAM讀和寫的時間控制。

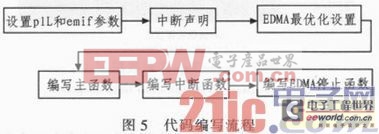

本論文中應用CCStudi03.1集成開發環境并結合C語言編寫DSP與FPGA的數據傳輸的代碼。編寫流程如圖5所示。

4 數據傳輸驗證

4 數據傳輸驗證

在設計中嵌入SignalTapⅡ邏輯分析儀有兩種方法:第一種方法是建立一個SignalTapⅡ文件(.stp),然后定義STP文件的詳細內容;第二種方法是用MegaWizard Plug-InManager建立并配置STP文件,然后用MegaWizard實例化一個HDL輸出模塊。圖6給出用這兩種方法建立和使用SignalTapⅡ邏輯分析儀的過程。

用QuartusII提供的Signal Tap仿真獲取數據,如圖7所示。

由SignalTap截獲的數據圖和RAM1中存儲的初始值對比可知,兩者之間的數值完全符合,由此可知DSP與FPGA的通信模塊能夠正常通信。

5 結論

文中設計了一種DSP和FFGA數據傳輸的通信模塊,通過Quartus II上完成了FPGA對數據采集系統的時序控制的設計,利用C語言編寫DSP與FPGA之間的通信控制代碼,應用Quartus II中的Signal Tap功能驗證了DSP與FPGA之間數據傳輸的正確性,證明該通信模塊能夠實驗電控噴油霧化檢測快速測量和處理大量的數據的要求。

fpga相關文章:fpga是什么

評論