基于FPGA+DSP的跳頻電臺傳輸系統

一個通信周期為80 ms,每1 ms容納32個基帶位(基帶速率為32 kbps)。

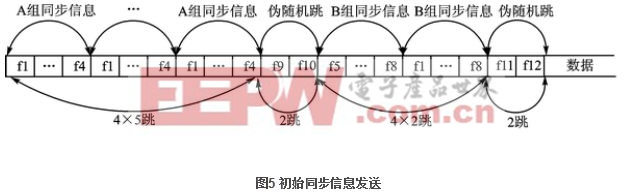

發端在按下PTT(Push To Talk)鍵時先發送一組同步頭,用來傳送初始同步信息,然后再發送語音信息。初始同步信息由初始同步頻率進行發送,根據發送的初始同步信息,初始同步頻率分成兩組,每組有4個同步頻率組成,為了提高同步的抗干擾性能,同步的頻率是隨著時間的變化而更新的。第一組頻率為f1、f2、f3、f4,每隔100個通信周期換掉一個同步頻率,用于傳送A組初始同步信息,傳送完A組同步信息后插入兩跳偽隨機跳頻(f9,f10)。第二組頻率為f5、f6、f7、f8,也是每隔100個通信周期換掉一個同步頻率,用于傳送B組初始同步信息,傳送完B組同步信息后插入兩跳偽隨機跳頻(f11,f12)。每次按下PTT鍵,發送32跳的初始同步信息,其發送格式如圖5所示。

正常跳頻通信時在語音跳中間加傳勤務同步跳,每800跳為一個通信循環,每80跳為一通信周期,每個通信周期傳4跳(f1,f2,f3,f4)勤務同步信息發送。

結語

基于FPGA的跳頻通信接收系統與常規跳頻通信接收系統相比,該系統具有靈活性強、可靠性高、開發周期短和費用低等優點,可廣泛應用于通信領域。在測試過程中發現本文設計的系統滿足性能要求:4.8kbps以下業務跳頻同步時間小于6s,4.8kbps以上業務跳頻同步時間小于0.6s。

評論