基于C6000系列DSP的MPEG-4編碼器實現

3.2 利用VLIW結構設計程序

利用VLIW結構設計程序可以充分利用DSP多個功能單元并行工作的特性。DSP的每一個通道都有四個功能單元(L、S、M、D),每個功能單元負責完成一定的邏輯或者算術運算,另外A、B兩個通道的互訪可以通過交叉單元1x、2x完成。程序2中,在一個時鐘周期內并行執行八條指令,使用了所有的功能單元S2、S1、L1、M2、L2、M1、D1、D2,同時使用了所有的交叉單元1x、2x,已經達到極限。但是這種并行指令的使用也有一定的限制,其最根本的要求就是不能引起資源沖突,例如:

·不能用同一個功能單元;

·不能對同一通道的寄存器進行兩次long型寫操作;

·不能對同一通道的寄存器同時進行long型讀操作和存儲操作;

·讀同一寄存器不能超過4次;

·在同一個時鐘周期不能有兩個指令寫入同一寄存器,這不是說向同一寄存器寫的兩條指令不能放在同一個并行指令包內,而是說兩個指令不能在寫寄存器的那個時鐘周期并存。

仍然以MPEG-4中的DCT算法為例說明VLIW結構在程序優化中的作用。進行DCT變換的原始數據是short型的,因此可以將兩個數據合成一個32位的數據來訪問;為了使兩個通道并行訪問數據和運算,應盡量把要訪問的數據平均地分配給不同的通道寄存器;并且通過交叉單元使兩個通道相互訪問,從而達到很高的并行性,大大提高了編碼效率。

MPEG-4編碼的其它算法,例如逆DCT、運動估計、運動補償等算法都包含著大量的循環運算和數據訪問。因此利用DSP的VLIW結構和流水線結構優化MPEG-4編碼算法就成為一種非常合適的方法。

當然,編寫程序時不是將DSP的VLIW結構和流水線結構分開考慮,而是將兩者結合起來,在編寫每一條指令時都要清楚這條指令的執行周期以及使用的功能單元,這樣才能編寫出高效的程序。

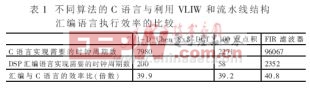

表1對1-D Chen 8×8 DCT、100點點積和FIR濾波器算法的C語言實現與利用VLIW及流水線結構的匯編代碼實現進行比較。從統計數據可以看出,利用DSP結構編寫的匯編代碼執行效率要比C語言編寫的代碼執行效率高40倍左右。因此充分利用DSP的VLIW結構和流水線結構設計匯編程序能夠使效率大幅度提高。

本文對MPEG-4編碼卡進行了設計,主要難點是MPEG-4編碼算法的優化,MPEG-4的編碼復雜、代碼量大。利用C6000系列DSP的VLIW結構和流水線結構設計出了MPEG-4編碼算法。實驗證明,算法效率得到了大幅度提高。

評論