新型直接數字下變頻器件AD6654在VHF跳頻電臺中的應用

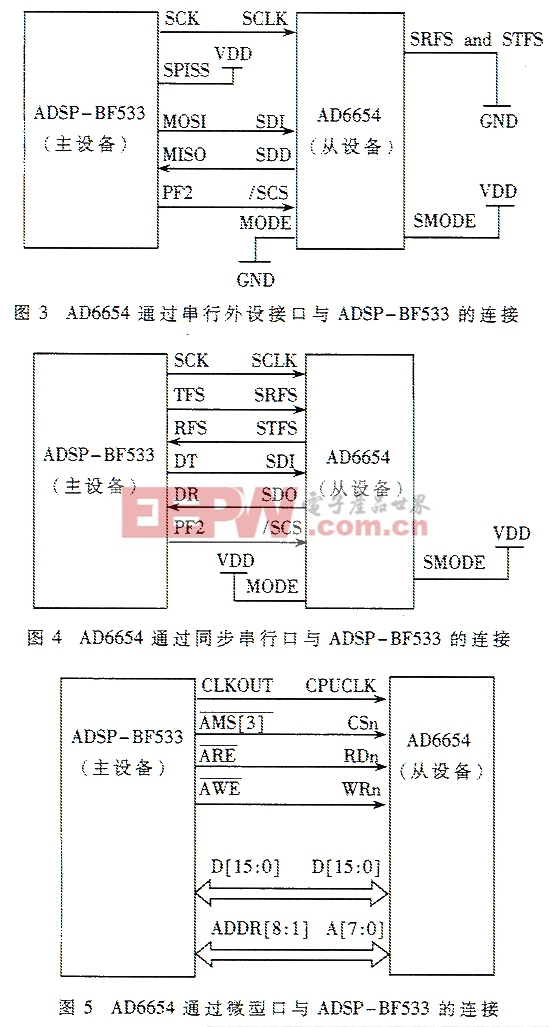

本系統在快跳頻中曾綜合考慮了多種非線性分集合并技術:自適應增益控制(AGC)合并、自歸一化合并(SNORM)、夾斷分集合并(CDC)、比率統計合并(RS)。其中AGC合并性能最好,但實現最難,其它幾種實現較容易。最終在語音部分,系統采用每個碼三個chip和自歸一化分集合并技術。該方法性能次佳,復雜度最低,可以顯著降低誤比特率。 以ADSP-BF533處理器為核心構成的快速跳頻電臺系統框圖如圖1和圖2所示。 在發送部分:ADSP-BF533對數據完成編碼、交織、偽隨機碼生成以及8FSK調制,經過數字上變頻器件AD9857生成跳頻發射信號。ADSP-BF533以6000次/秒的頻率更新AD9857輸出的跳變信號。用GOLD序列產生一組偽隨機碼,然后以此偽隨機碼產生一組跳變頻點,再與8FSK調制信息相結合,采用跳頻數字調制方法,得到正弦波振蕩輸出。 在接收部分:接收射頻信號經過AD6654后直接變換到基帶,以16位方式并行輸出。首先ADSP-BF533控制AD6654在一個定頻上等待同步頭,進入DSP同步擁獲程序;一旦捕獲到同步信號,DSP即啟動跳頻碼序列發生器,控制查詢跳頻圖案表產生DDS控制字,由該控制字查詢預先存儲在存儲器中的正弦表,產生與發射機同步跳變的載波信號。待跳頻同步后,將跳頻的基帶FSK信號解調出來,然后進行解交織,并經維特比譯碼后輸出信息。上述跳頻同步跟蹤以及信道譯碼過程均在ADSP-BF533中完成。圖63 ADSP-BG533與AD6654的幾種連接方式 AD6654具有8/16位微型口、串行外設接口、同步串口控制接口,頻率控制字可以通過上述三種方式寫入,但同一時刻只能采用一種方式進行控制。AD6654的微型口可以工作在兩種不同模式下:Intel模式(MODE=0,SMODE=0)和Motorola模式(MODE=1,SMODE=0)。Intel模式采用獨立的讀/寫低有效使能信號控制讀寫操作,Motorola模式采用單一的R/W信號控制讀寫操作,AD6654設置上述兩種模式可以靈活地與多種微處理器實現無縫連接。 圖3、圖4、圖5分別為ADSP-BF533通過串行外設接口、同步串口、微型口與AD6654進行連接的典型方式。其中,ADSP-BF533是主設備,AD6654是從設備。 在圖3中,ADSP-BF533的SCK是輸出時鐘;SPISS是主設備從設備選擇信號,SPISS置低使能ADSP-BF533為從設備,SPISS置高使能ADSP-BF533為主設備,在這里ADSP-BF533作為主設備使用,因此置為高電平,接VDD(3.3V);MOSI是主設備輸出/從設備輸入引腳,在這里作為發送數據引腳;MISO是主設備輸入/從設備輸出引腳,在這里作為數據輸入引腳;通用I/O引腳PF2作為片選信號,與AD6654片選信號/SCS相連。AD6654的SDI是串行數據輸入線,SDO是串行數據輸出線,SCLK是時鐘信號,STFS和SRFS分別是發送和接收幀同步信號,置為低電平,接GND,即默認為已同步。 在圖4中,ADSP-BF533的SCK是輸出時鐘,TFS、RFS是發送和數據收的幀同步信號,DT和DR分別是發送和接收的數據。AD6654的SCLK是時鐘輸入信號,STFS和SRFS分別是發送和接收的幀同步信號,它們的引腳分別與ADSP-BF533的RFS、TFS引腳相連,SDO和SDI分別是輸出和輸入的數據。ADSP-BF533的通用I/O信號PF2作為片選信號,其引腳與AD6654的片選信號/SCS引腳相連。

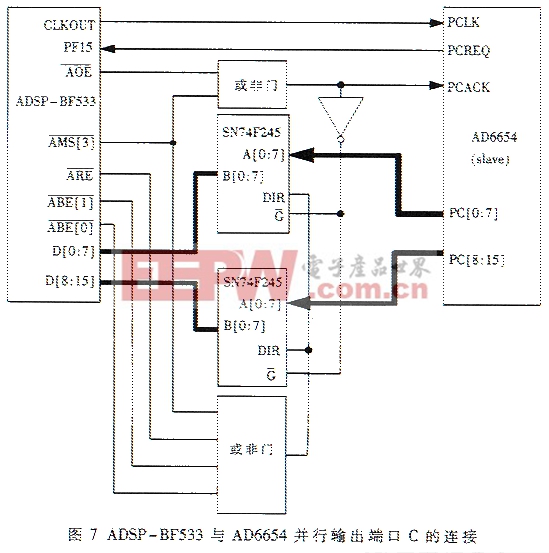

本系統在快跳頻中曾綜合考慮了多種非線性分集合并技術:自適應增益控制(AGC)合并、自歸一化合并(SNORM)、夾斷分集合并(CDC)、比率統計合并(RS)。其中AGC合并性能最好,但實現最難,其它幾種實現較容易。最終在語音部分,系統采用每個碼三個chip和自歸一化分集合并技術。該方法性能次佳,復雜度最低,可以顯著降低誤比特率。 以ADSP-BF533處理器為核心構成的快速跳頻電臺系統框圖如圖1和圖2所示。 在發送部分:ADSP-BF533對數據完成編碼、交織、偽隨機碼生成以及8FSK調制,經過數字上變頻器件AD9857生成跳頻發射信號。ADSP-BF533以6000次/秒的頻率更新AD9857輸出的跳變信號。用GOLD序列產生一組偽隨機碼,然后以此偽隨機碼產生一組跳變頻點,再與8FSK調制信息相結合,采用跳頻數字調制方法,得到正弦波振蕩輸出。 在接收部分:接收射頻信號經過AD6654后直接變換到基帶,以16位方式并行輸出。首先ADSP-BF533控制AD6654在一個定頻上等待同步頭,進入DSP同步擁獲程序;一旦捕獲到同步信號,DSP即啟動跳頻碼序列發生器,控制查詢跳頻圖案表產生DDS控制字,由該控制字查詢預先存儲在存儲器中的正弦表,產生與發射機同步跳變的載波信號。待跳頻同步后,將跳頻的基帶FSK信號解調出來,然后進行解交織,并經維特比譯碼后輸出信息。上述跳頻同步跟蹤以及信道譯碼過程均在ADSP-BF533中完成。圖63 ADSP-BG533與AD6654的幾種連接方式 AD6654具有8/16位微型口、串行外設接口、同步串口控制接口,頻率控制字可以通過上述三種方式寫入,但同一時刻只能采用一種方式進行控制。AD6654的微型口可以工作在兩種不同模式下:Intel模式(MODE=0,SMODE=0)和Motorola模式(MODE=1,SMODE=0)。Intel模式采用獨立的讀/寫低有效使能信號控制讀寫操作,Motorola模式采用單一的R/W信號控制讀寫操作,AD6654設置上述兩種模式可以靈活地與多種微處理器實現無縫連接。 圖3、圖4、圖5分別為ADSP-BF533通過串行外設接口、同步串口、微型口與AD6654進行連接的典型方式。其中,ADSP-BF533是主設備,AD6654是從設備。 在圖3中,ADSP-BF533的SCK是輸出時鐘;SPISS是主設備從設備選擇信號,SPISS置低使能ADSP-BF533為從設備,SPISS置高使能ADSP-BF533為主設備,在這里ADSP-BF533作為主設備使用,因此置為高電平,接VDD(3.3V);MOSI是主設備輸出/從設備輸入引腳,在這里作為發送數據引腳;MISO是主設備輸入/從設備輸出引腳,在這里作為數據輸入引腳;通用I/O引腳PF2作為片選信號,與AD6654片選信號/SCS相連。AD6654的SDI是串行數據輸入線,SDO是串行數據輸出線,SCLK是時鐘信號,STFS和SRFS分別是發送和接收幀同步信號,置為低電平,接GND,即默認為已同步。 在圖4中,ADSP-BF533的SCK是輸出時鐘,TFS、RFS是發送和數據收的幀同步信號,DT和DR分別是發送和接收的數據。AD6654的SCLK是時鐘輸入信號,STFS和SRFS分別是發送和接收的幀同步信號,它們的引腳分別與ADSP-BF533的RFS、TFS引腳相連,SDO和SDI分別是輸出和輸入的數據。ADSP-BF533的通用I/O信號PF2作為片選信號,其引腳與AD6654的片選信號/SCS引腳相連。 在圖5中,ADSP-BF533通過外部總線接口單元(EBIU)與AD6654相連。在ADSP-BF533中,CLKOUT是輸出時鐘信號,AMS[3]是異步存儲器選擇信號,AWE和ARE是異步存儲器寫使能和讀使能信號,ABE[1:0]是字節使能信號(沒有使用),D[15:0]是16位數據信號,ADDR[8:1]是地址信號。在AD6654中,CPUCLK是微型口的時鐘輸入信號,CSn是片選信號,RDn和WRn分別是讀和寫信號。 通過微型口、串行外設接口以及同步串口,ADSP-BF533可以訪問AD6654的內部寄存器,直接查詢下變頻的輸出結果,但無法確定數據何時開始更新,因此對于跳頻通信而言,下變頻后的數據需要從并行輸出口實時輸出。考慮到ADSP-BF533的特點,本系統采用串行外設接口控制AD6654和16位并行接口輸出數據的方式完成從射頻到基帶信號的轉換。 4 ADSP-BF533與AD6654的16位并行輸出端口的連接 AD6654具有三個16位可配置的并行輸出端口,即A、B、C端口,可以工作在主從兩種模式,I/Q數據可以選擇交織或并行方式輸出,數據位數可以選擇8位或16位方式,自動增益(AGC)控制字可以選擇是否輸出。圖6是AD6654從模式8位并行I/Q輸出時序圖。圖中,PCLKn是AD6654的輸入時鐘信號,PxACK是并行口確認信號,PxREQ是并行口請求信號,Px[15:0]是并行輸出端口數據,PXIQ是并行端口I/Q數據標記信號(高電平表示I路數據,低電平表示Q路數據),PXCH[2:0]是輸出端口信道標記信號,PXGAIN是并行口AGC輸出標記信號。AD6654并行輸出口與ADSP-BF533異步外設接口的連接方法如圖7所示。 在圖7中,CLKOUT是ADSP-BF533的輸出時鐘信號,由內部主時鐘分頻產生,送到AD6654的時鐘PCLK輸入端。在該電路板初始化時,首先向ADSP-BF533控制寄存器寫入命令,使得ADSP-BF533讀取數據時的插入等狀態為零,與AD6654工作時序完全匹配。在AD6654完成數字下變頻時,向ADSP-BF533發出讀取請求信號PCREQ,該信號在高電平時有效,通過ADSP-BF533的能家長I/O管腳PF15產生中斷,由中斷服務程序完成8位I/Q數據的讀取。圖中AOE是ADSP-BF533的異步存儲器輸出使能信號,該信號為低時表示讀周期開始,AMS[3]、AOE經過或非門產生確認信號,送往AD6654的PCACK管腳,同時它的反射信號送往SN74F245的使能端G。AMS[3]是ADSP-BF533的異步存儲器選擇信號,(ADSP-BF533共有四塊異步存儲區,AMS[3]選擇0x2030000~0x203FFFFF地址單元空間);ARE是ADSP-BF533的異步存儲器讀信號,ABE[0]/ABE[1]是字節使能輸出信號,上述四個信號經或非電路產生SN74F245的讀控制信號DIR。為簡化設計,ADSP-BF533的地址線ADDR[19:1]沒有參與譯碼。

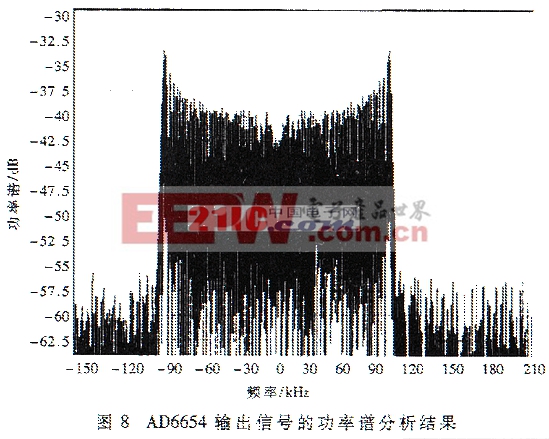

在圖5中,ADSP-BF533通過外部總線接口單元(EBIU)與AD6654相連。在ADSP-BF533中,CLKOUT是輸出時鐘信號,AMS[3]是異步存儲器選擇信號,AWE和ARE是異步存儲器寫使能和讀使能信號,ABE[1:0]是字節使能信號(沒有使用),D[15:0]是16位數據信號,ADDR[8:1]是地址信號。在AD6654中,CPUCLK是微型口的時鐘輸入信號,CSn是片選信號,RDn和WRn分別是讀和寫信號。 通過微型口、串行外設接口以及同步串口,ADSP-BF533可以訪問AD6654的內部寄存器,直接查詢下變頻的輸出結果,但無法確定數據何時開始更新,因此對于跳頻通信而言,下變頻后的數據需要從并行輸出口實時輸出。考慮到ADSP-BF533的特點,本系統采用串行外設接口控制AD6654和16位并行接口輸出數據的方式完成從射頻到基帶信號的轉換。 4 ADSP-BF533與AD6654的16位并行輸出端口的連接 AD6654具有三個16位可配置的并行輸出端口,即A、B、C端口,可以工作在主從兩種模式,I/Q數據可以選擇交織或并行方式輸出,數據位數可以選擇8位或16位方式,自動增益(AGC)控制字可以選擇是否輸出。圖6是AD6654從模式8位并行I/Q輸出時序圖。圖中,PCLKn是AD6654的輸入時鐘信號,PxACK是并行口確認信號,PxREQ是并行口請求信號,Px[15:0]是并行輸出端口數據,PXIQ是并行端口I/Q數據標記信號(高電平表示I路數據,低電平表示Q路數據),PXCH[2:0]是輸出端口信道標記信號,PXGAIN是并行口AGC輸出標記信號。AD6654并行輸出口與ADSP-BF533異步外設接口的連接方法如圖7所示。 在圖7中,CLKOUT是ADSP-BF533的輸出時鐘信號,由內部主時鐘分頻產生,送到AD6654的時鐘PCLK輸入端。在該電路板初始化時,首先向ADSP-BF533控制寄存器寫入命令,使得ADSP-BF533讀取數據時的插入等狀態為零,與AD6654工作時序完全匹配。在AD6654完成數字下變頻時,向ADSP-BF533發出讀取請求信號PCREQ,該信號在高電平時有效,通過ADSP-BF533的能家長I/O管腳PF15產生中斷,由中斷服務程序完成8位I/Q數據的讀取。圖中AOE是ADSP-BF533的異步存儲器輸出使能信號,該信號為低時表示讀周期開始,AMS[3]、AOE經過或非門產生確認信號,送往AD6654的PCACK管腳,同時它的反射信號送往SN74F245的使能端G。AMS[3]是ADSP-BF533的異步存儲器選擇信號,(ADSP-BF533共有四塊異步存儲區,AMS[3]選擇0x2030000~0x203FFFFF地址單元空間);ARE是ADSP-BF533的異步存儲器讀信號,ABE[0]/ABE[1]是字節使能輸出信號,上述四個信號經或非電路產生SN74F245的讀控制信號DIR。為簡化設計,ADSP-BF533的地址線ADDR[19:1]沒有參與譯碼。 5 AD6654電路板實測結果 在VHF跳頻電臺的研制過程中,采用AD6654作為接收機前端,省去多級混頻結構,進一步簡化了設計,同時有利于高速跳頻接收機的實現。在調試過程中,AD6654輸入的射頻信號為調頻波,采用100kHz的正弦波對70MHz載波信號進行FM調制,經過AD6654下變頻處理后,得到數字基帶信號,然后對基帶信號進行功率譜分析,處理結果如圖8所示。從測試結果看,經AD6654處理后的信噪比達到20dB以上。在現場測試試驗中,ADSP-BF533與AD6654接口板的電路工作穩定,性能指標達到設計要求。

5 AD6654電路板實測結果 在VHF跳頻電臺的研制過程中,采用AD6654作為接收機前端,省去多級混頻結構,進一步簡化了設計,同時有利于高速跳頻接收機的實現。在調試過程中,AD6654輸入的射頻信號為調頻波,采用100kHz的正弦波對70MHz載波信號進行FM調制,經過AD6654下變頻處理后,得到數字基帶信號,然后對基帶信號進行功率譜分析,處理結果如圖8所示。從測試結果看,經AD6654處理后的信噪比達到20dB以上。在現場測試試驗中,ADSP-BF533與AD6654接口板的電路工作穩定,性能指標達到設計要求。

評論