一種通用的FPGA網絡下載器硬件設計

但在實際設計中,由于疊層的設計,不可能單獨列出較多層,對于TTL和LVDS信號的地層也無需進行分割,因其會破壞地層的完整性,在確保完整地的情況下,可對其他地層TTL和LVDS信號分割。總之,在保證地層完整的情況下,使LVDS信號和TTL信號盡量分離,最好是在不同的層進行布線。在本PCB板的設計中,使用6層疊層結構:TOP-GND1-INNER-POWER-GND2-BOTTOM,其中TOP和BOTTOM層走LVDS信號,INNER和GND2走LVTTL信號,這樣既保持了信號的分層,也保持了完整的信號回流路徑。

本文引用地址:http://cqxgywz.com/article/249137.htmLVDS信號頻率可達600 MHz以上,所以差分線要求嚴格等長,差分對內最好不超過10 mil(0.254mm),若頻率低于600 MHz,該約束值可適當放寬,但上限不能超過75 mil。不同LVDS對間的布線最大差值不超過200 mil。文中在Cadence16.3的約束設置中,具體設置如下。

差分阻抗的不匹配會產生反射,有10%的阻抗不匹配便會產生5%的反射,所以需根據不同的情況進行不同的匹配控制。LVDS信號的差分特性阻抗為100 Ω,對于LVDS信號發射端(TX),采用差分對各自串聯精度為1%的50 Ω電阻進行匹配,這樣既保持了信號傳輸的功率要求,又滿足了阻抗控制的要求。

4 實測結果

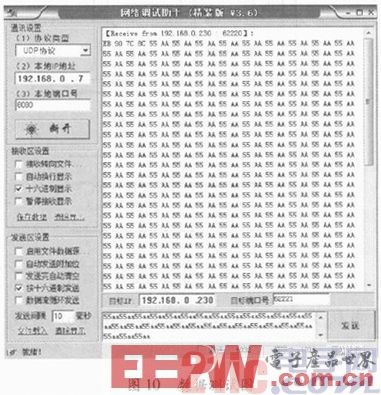

下載器性能實測時,將LVDS接口接收和發送部分回環連接,可使用網絡調試助手發送55 AA組成的1 032 Byte的數據包,測試下載器的功能。結果如圖10所示,從圖中可看到,下載器穩定的收發數據。

5 結束語

設計的網絡下載器將FPGA在信號處理中的優勢和ARM芯片在網絡通信中的優勢相結合,在PCB設計中對于LVDS接口的阻抗、高速線時序以及疊層進行了設計,較好地保證了系統硬件的可靠性,并在實際使用中達到了良好的效果。

fpga相關文章:fpga是什么

評論