2 基于FPGA的DDS信號發生器的設計

該信號發生器是作為電路板檢測儀的激勵信號源,產生的信號分別為:頻率為16 000±0.8 Hz的正弦波,頻率為128 000±* Hz,64 000±3.2 Hz,4 000±O.2 Hz的方波和周期為10μs,占空比為1:4的脈沖信號。下面以正弦波的產生為例說明DDS的實現過程。當f0=16 000 Hz,N=16時,根據式(1),則K=104。

2.1 相位累加器

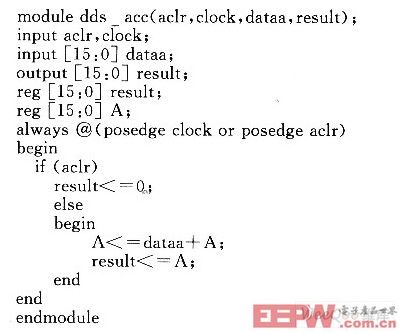

相位累加器主要是根據頻率控制字生成ROM查找表的地址,采用硬件描述語言Verilog DHL實現,其源程序為:

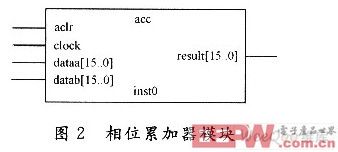

文本輸入完畢后,用QuartusⅡ進行編譯,然后生成.bsf文件,以便在頂層設計時調用。其生成頂層模塊如圖2所示。

評論