基于IBM GPM模型的DDR2接口信號完整性分析

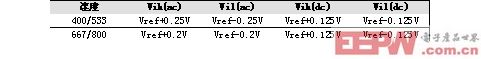

其中,JEDEC標準里規定了Vih(ac/dc)和Vil(ac/dc),如表2所示。

表2 Vih/Vil的ac和dc值

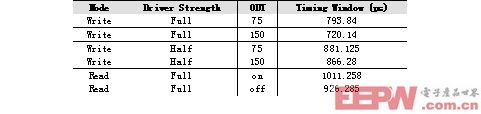

通過配置不同讀寫模式,驅動能力和片上端接電阻對有效時序窗口大小的分析,我們可以得到關于時序最優的解決方案。表3是用GPM模型對這幾種情況下分析的結果:

表3 各種情況下Timing Window

從表3可以看出,在“寫”的情況下,驅動能力為“Half”,ODT為75ohm端接時,時序有效窗口最大,相應的建立時間和保持時間的裕量最大;在“讀”的情況下,同是“Full”強驅動,打開ODT和關閉ODT也會有不同的效果,前者會更好。

5. 結論

1)本文通過實例介紹了基于GPM的DDR2 高速接口的設計和仿真,接口信號完整性與封裝結構、芯片布局、IO類型、板級走線、驅動負載緊密相關,我們可以通過系統應用的實際需求進行設計和仿真。

2)由于GPM的建模對設計文件的依賴性較少,所以在進行芯片布局的同時就可以開始進行模型的建立和分析,對芯片的布局設計提供了很好的指導,并成為芯片電源噪聲的簽收標準之一。

3)GPM可以導入客戶的PCB互聯模型,用于對IO的時序和信號完整性進行分析。模型中包含了電源網絡的信息,仿真得到的結果也包含了SSN的信息,更加接近實際的應用環境。可以用于能指導ASIC的設計團隊完成IO的時序收斂,客戶PCB的系統設計。

4)GPM模型中IO的模型采用IBM自行研發的IO buffer的SPICE模型,對各種高速接口(如DDR2)的建模與仿真,可以達到非常高的精度。同時,GPM 仿真可以在設計初期對芯片、封裝和板級設計提供指導,從而極大的減少整個系統設計和驗證的周期。

附:本文僅代表個人觀點,IBM不保證文中推薦解決方案在其他設計上的應用。

參考文獻:

1) JESD79-2C DDR2 SDRAM SPECIFICATION

2) IBM ASIC Generic Package Models

3) Mitigating Transient Noise ASIC Solutions Application Note: SA15-5889-02

4) On-Chip Decoupling Capacitor Guidelines Application Note: SA15-5919-13

評論