一種DSP內嵌DARAM的電路設計與ADvance MS仿真驗證

存儲陣列的結構如圖10。存儲單元為常用的6管SRAM單元,進行讀寫操作時,OE由低變高,預充電管關閉,通過讀寫放大器對位線的充電與放電來實現數據讀寫。

本文引用地址:http://cqxgywz.com/article/255835.htm3 仿真驗證

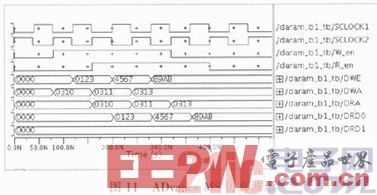

為了使仿真結果準確,輸入波形應該與實際情況一致,先用ModelSim對整體DSP芯片進行仿真,然后觀察DARAM的輸入端,按照所得的輸入信號再單獨對DARAM進行仿真,由于電路中既有數字電路也有模擬電路,所以采用數模混合仿真的方法,用ADvance MS對該電路進行仿真。仿真波形如圖11。

在4個時鐘周期內,對DARAM進行三次寫操作和三次讀操作,數據在SCLOCK2上升沿時寫入,在SCLOCK1上升沿時讀出,在第二個周期與第三個周期內,W_en和R_en同時使能,也就是要在一個周期內進行兩次操作,進行“雙存取”。從兩塊存儲陣列中讀出的數據分別為DRD0和DRD1,可以看出,DRD0依次讀出的三組數據0123H、4567H和89ABH即為前一周期寫入的數據,說明此電路可以正確的讀寫數據,也可以在一個周期內完成一次讀操作和一次寫操作。

4 結束語

本文以一款國外公司的DSP為例,介紹了其內嵌的一塊DARAM的整體電路,給出了關鍵部分的具體電路,并結合仿真波形,詳細介紹了電路的工作原理,最后采用數模混合仿真的方法,用ADvance MS對整體的電路進行仿真,結果證明此電路可以實現一個周期內的“雙存取”功能,可以為DSP乃至SOC中存儲器接口電路的設計提供一種參考。

存儲器相關文章:存儲器原理

脈沖點火器相關文章:脈沖點火器原理

評論