基于LVDS的高速圖像數據存儲器的設計與實現

3)操作簡單。首先,單片64 kbyte CY7CA285V就可以滿足設計要求,而不需串聯多個FIFO,這樣操作起來方便了很多。其次,該FIFO有讀使能、寫使能作為狀態保障,且均采用邊沿觸發方式,使得時序控制簡捷高效,便于FPGA的邏輯實現。

3關鍵技術研究

3.1高速寫入方式

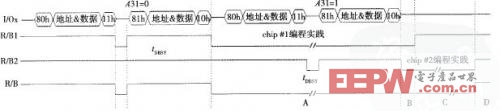

本設計選用三星公司的K9WBG08U1M作為存儲介質。該芯片容量大小為4 Gbyte,內部分為2片,每片2 Gbyte,可通過片選信號和切換兩片存儲空間,每片由8192塊組成,每塊中有64頁,每一頁都可以存儲4 kbyte的圖像數據和128 byte的狀態信息。本設計要完成對高速圖像數據的存儲任務,普通的Flash寫入方式無法滿足30.72 Mbyte/s.數據存儲速度的要求。因此,大幅提高Flash數據接口的寫入速度,成為系統設計的關鍵。K9WBG08U1M內部平面結構圖如圖5所示,Flash內部的兩片分別為chip1和chip2,4個平面Plane0~Plane3組成1個chip,原始的寫入方式為依次寫滿Plane0、Plane1、Plane2、Plane3,為大幅度提高數據存儲速度,系統采用交錯雙平面頁編程(interleave two-plane page program)的操作方式,并行對chip1、chip2的8個平面進行操作,如圖6所示Interleave two-plane編程時序圖:從chip1的Plane0開始依次寫入每一個平面第1塊的第1頁,即寫入chip1的Plane0的block0的page0后,再橫向連續寫入7頁,那么當循環回chip1的Plane0的block0的page1時,用時25 ns x 4096 x 7=716.8μs大于頁編程時間tPRoG的最大值700μs,從而可以不問斷地繼續對chip1的Plane0的block0的page1進行操作,這樣充分利用了頁編程的時間,使Flash的寫入速度提高到40 Mbyte/s,完全可以完成對30.72 Mbyte/s圖像數據的存儲任務。

圖5 K9WBG08U1M內部平面結構圖

圖6 Interleave two-plane編程時序圖

3.2圖像數據分析

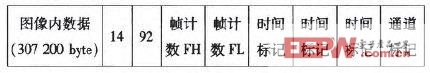

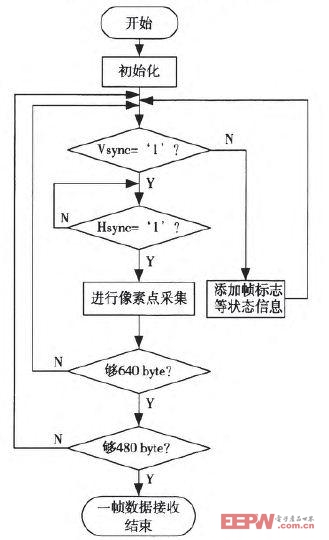

在飛行中該圖像存儲器需要在過載、噪聲等惡劣環境下工作,由于這些干擾很可能丟失一幀或者若干幀數據,為此本文經分析接收圖像時序,為圖像數據編幀如圖7.這樣將圖像數據設定成固定的幀格式,不僅可以穩定地循環采集,便于數據處理;而且即使由于干擾丟掉了一幀或若干幀,也不會影響幀結構的完整性,對于整體數據分析沒有影響。這樣就保證了后續存儲轉發數據的正確性。接收一幀圖像數據的流程圖如圖8所示。

圖7圖像存儲數據幀結構

圖8接收一幀圖像數據流程圖

3.3圖像信息存儲設計

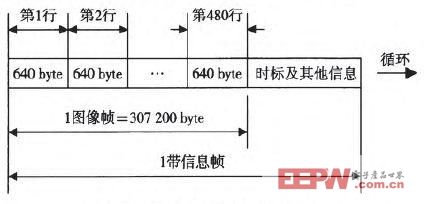

如圖9所示待存儲數據的數據流結構,1帶信息幀由1圖像幀和時標及其他信息組成,存入Flash的為帶信息幀,但后續轉發給圖像壓縮單元的數據只能含有圖像幀。為此本文將FIFO設計成9位緩存模式,低8位用來存儲圖像數據圖像幀或時暢汲其他信息,最高位通過“1”或“0”來區分是圖像數據還是幀標志。即將低8位是圖像數據的最高位置高,低8位是時標及其他輔助信息的最高位置低,轉發時只將最高位為1的數據流發送給圖像壓縮單元。

圖9待存儲數據的數據流結構

一片K9WBG08U1M的Flash內部有1048576頁,本文所接收的圖像數據:1圖像幀=307 200 byte,1頁容量為4 kbyte,需用75頁,所以1片Flash最多可存儲13981幀視頻圖像。接收圖像幀頻為100 f/s,25s接收2500幀視頻圖像,僅占Flash總容量的1%.采用上述interleavetwo-plane page program的頁編程方式,每75頁代表一幀視頻圖像數據,第76頁用來寫入每一幀的狀態信息。寫入的順序如圖10中箭頭所示。

圖10存儲區和圖像幀之間的映射關系

存儲器相關文章:存儲器原理

評論