ARM體系結構的發展之:ARM體系結構的發展過程

16.1ARM體系結構的發展過程

隨著片上系統設計變得更加精密、復雜,ARM處理器已成為包含多個處理部件和子系統的系統核心處理器。每個ARM處理器都有一個特定的指令集架構ISA,ISA隨著嵌入式市場的需求而發展。每一個ISA的發布都是相后兼容的,這使得在較早的架構版本上編寫的代碼也可以在后續版本上執行。

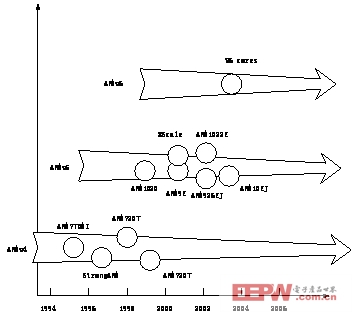

本文引用地址:http://cqxgywz.com/article/257008.htm圖16.1說明了ISA的發展過程。

圖16.1ISA發展過程

ISA的每一次發展,體現在命名上,就是在版本名稱中增加新的變量。ISA的發展分下面幾個過程。

①V3架構中引入了32-bit尋址和16-bit指令執行,而且在版本號中增加了變量T和變量M其中:

·T變量:16bit指令執行。

·M變量:長乘法的支持。

②V4中增加半字Load/Store指令。

③V5中增加ARM/Thumb交互工作機制,而且在版本號中增加了變量E和變量J其中,

·E變量:增強的DSP指令。

·J變量:Jazelle狀態。

注意 | 所有這些“TEJ”變量特性都集成在ARMv6體系結構中。 |

ARM面臨的挑戰是要滿足不斷變化的市場需求,同時在計算效率方面,繼續保持工業界最強的競爭優勢。

評論