ARM存儲器之:存儲保護單元MPU

(3)c3中的MPU相關位

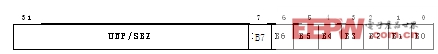

c3的編碼格式如圖15.20所示。

圖15.20協處理器寄存器c3編碼格式

寄存器位0~7分別對應域0~7的寫緩存屬性。位8~31應該設置成0。

當用指令MCR/MRC對c3進行讀寫時,第二個操作數opcode2>將被忽略,在指令要設置成0。

當配置數據域時,域的Cache位和寫緩存區位一起決定域的訪問策略。寫緩存位有兩個用途:使能/禁止域的寫緩存和設置域的Cache寫策略。域的Cache位控制寫緩存位的作用。具體位分配見表15.16。

表15.16 Cache位和寫緩存位的分配策略

Cache位 | 寫緩存區位 | 域屬性 |

C=0 | B=0 | 禁止Cache、禁止寫緩存 |

C=0 | B=1 | 禁止Cache、使能寫緩存 |

C=1 | B=0 | 使能Cache,域使用回寫策略 |

C=10 | B=1 | 使能Cache,域使用直寫策略 |

(4)訪問權限寄存器c5

協處理器CP15的寄存器c5設置內存域的訪問權限。

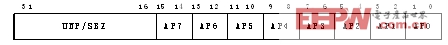

寄存器c5的編碼格式如圖15.21所示。

圖15.21寄存器c5的編碼格式

讀寄存器c3的bits[15:0]存放域的AP(accesspermission,訪問權限),其中bits[2n+1:2n]對于域n的訪問權限。AP編碼與訪問權限的對應關系如表15.17所示。

表15.17 AP編碼與訪問權限的對應關系

AP編碼 | 管理者 | 用戶 |

00 | 不可訪問 | 不可訪問 |

01 | 讀/寫 | 不可訪問 |

10 | 讀/寫 | 只讀 |

11 | 讀/寫 | 讀/寫 |

對于Arm940T、Arm940T兩個內核版本來說,使用MRC和MCR指令對其進行讀寫時,第二個協處理器寄存器CRm>將被忽略,指令中以c0的形式出現。對于指令數據統一的域,第二操作數opcode2>要設成0,而對于數據和指令分離的系統,如果opcode2=0,說明操作對數據域有效,如果opcode=1,說明操作對指令域有效。

| 注意 | 對于Arm946E-S和Arm1026EJ-S兩個內核版本,它們的訪問權限機制更復雜,采用的是擴展AP,擴展組AP位域編碼支持兩個增強的權限域,對其進行操作的MRC和MCR指令形式更復雜,有關更詳細的內容,請參加Arm公司的用戶手冊。 |

(5)域大小控制寄存器c6

Arm系統中通過寫協處理器c6來定義域的大小,通過MCR指令中第二個操作寄存器賦不同的值來指示是對哪個具體域進行操作。第二個操作寄存器取值為c0~c7,分別對應域0~域7。

每個域的起始地址必須對齊到其大小的整數倍。比如,一個域的大小位64KB,其起始地址可以是0x10000的整數倍的任何數。域的大小可以是4KB~4GB的2的任意乘冪。

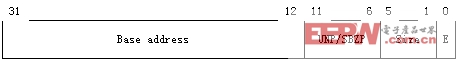

寄存器c6的編碼格式如圖15.22所示。

圖15.22域大小控制寄存器c6編碼格式

存儲器相關文章:存儲器原理

評論