一種3dB帶狀線耦合電橋的研究與設計

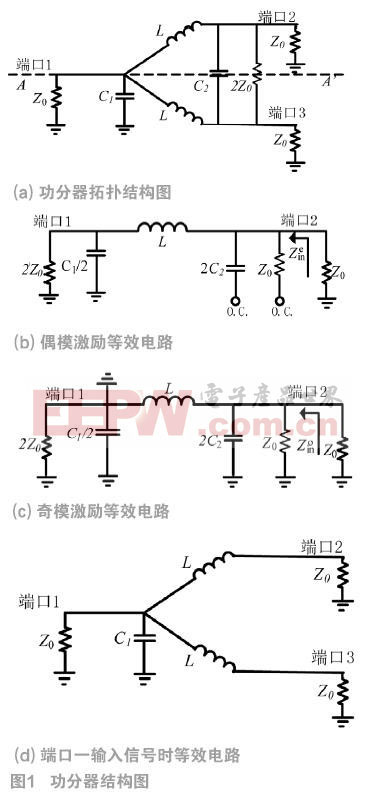

3耦合器的設計

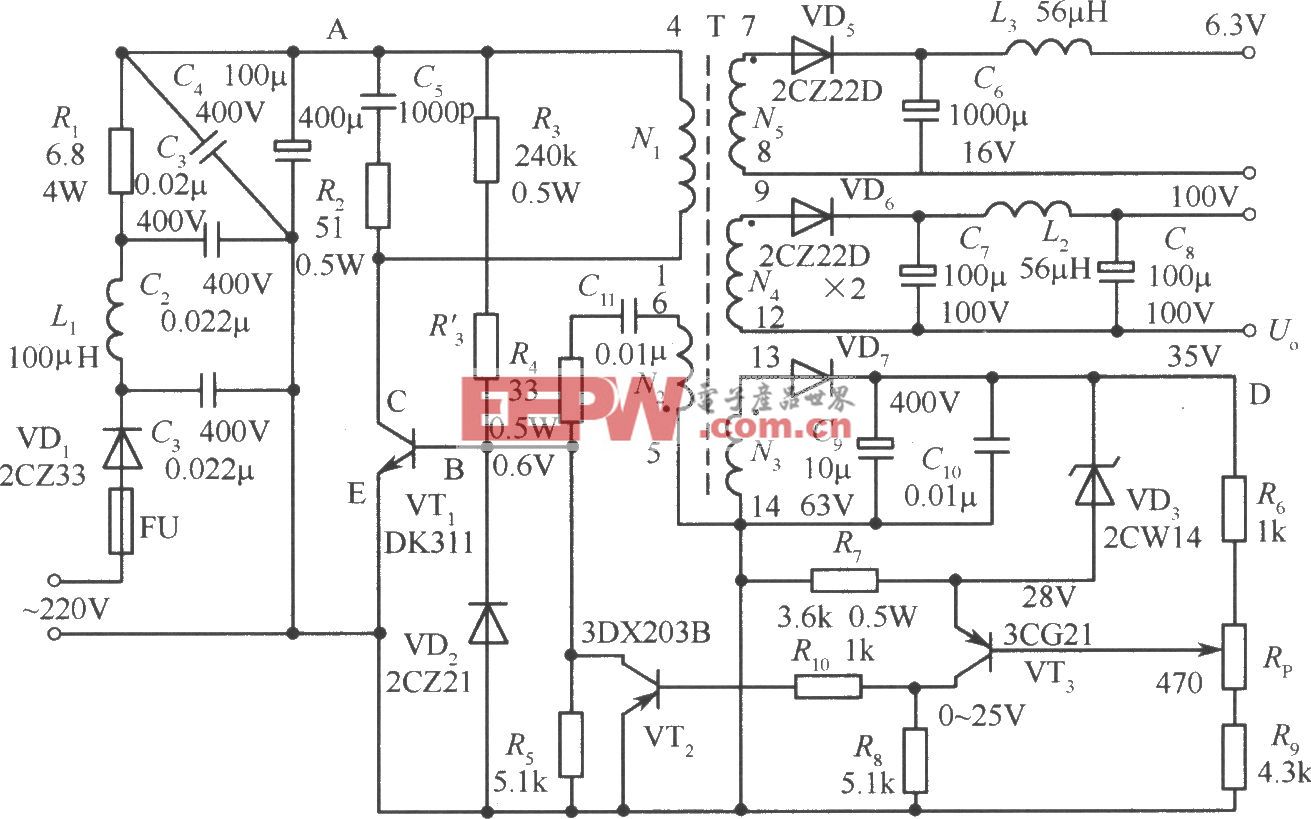

單個λ/4帶狀線耦合器。如下圖4說是信號由1口輸入時,2口為隔離端口,3口為耦合端口,4口為直通端口。這種結構由于直通端和耦合輸出端在同一個方向,方便連接和實現級聯。在帶狀線耦合器設計中已經得到廣泛的采用。

圖4單個λ/4帶狀線耦合器

采用該方法一共需要用三塊材料相同的介質基片和兩層金屬微帶線。分別將它們按照一定的結構疊起來。從下往上依次是:下接地板、介質層、金屬微帶層、介質層、金屬微帶層、介質層和上接地板。在實際設計中我們可以通過調節λ/4帶狀線重疊部分的大小來調節耦合度。

本次設計的指標如下

頻率 | 10GHz±1GHz |

駐波 | ≤1.5 |

隔離 | ≥20dB |

插入損耗 | ≤1dB |

帶內幅度起伏 | ≤0.5dB |

相位起伏 | ≤5° |

介質板 | Rogers5880 h=0.254mm |

接口形式 | SMA |

通過HFSS電磁仿真軟件對耦合器進行仿真,由于單個λ/4帶狀線耦合器在兩條微帶線完全重疊實現最大耦合度的條件下很難實現3dB的要求。為了完成上述設計指標選擇采用兩個λ/4耦合線寬邊耦合器級聯來實現該電橋,如圖3所示。

圖5級聯耦合器

評論