基于FPGA的16抽頭FIR數字低通濾波器設計與仿真

4.4 移位累加模塊

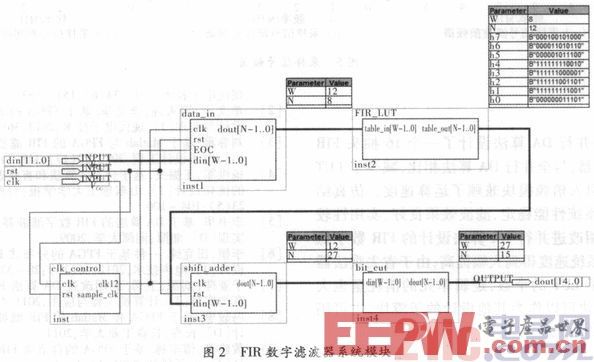

本文引用地址:http://cqxgywz.com/article/262694.htm系統核心模塊,主要對查找表模塊輸出數據進行移位累加操作,由于輸入12位數據,因此要進行12次移位操作,前11次移位進行加法操作,第12次移位進行減法操作。為使累加結果不溢出,要進行冗余設計。

若輸入數據與濾波器系數均為B位,對于有符號系統,移位累加器長度M=2B+log2N-1,其中N為濾波器抽頭數。該移位累加模塊輸出數據寬度為27位。

4.5 截位模塊

移位累加模塊輸出27位數據,由于其對應的10進制數值較大,不便于分析,因此對移位累加模塊的輸出數據進行截位。截位模塊的功能是通過移位截取27位輸入數據的高15位。

5 Matlab與QuartusII聯合仿真

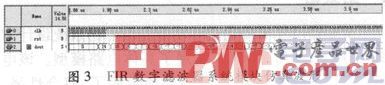

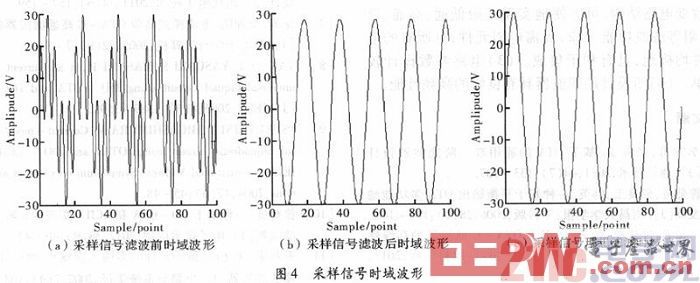

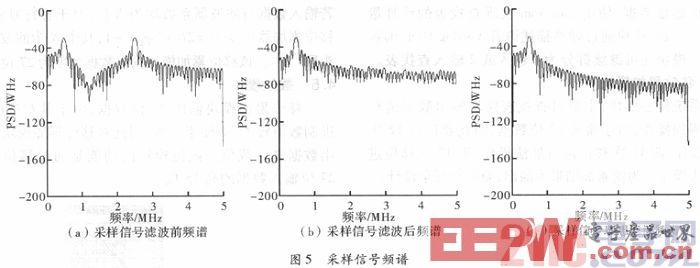

FIR數字濾波器輸入與輸出均是數字信號,通過Matlab編程模擬A/D轉換得到濾波器輸入數據,然后將輸入數據送到濾波器輸入端口并進行仿真得到輸出波形,最后再通過Matlab編程模擬D/A轉換將輸出數字信號以模擬信號波形形式展現。具體步驟如下:首先利用Matlab編寫得到*.mif文件的M程序,輸入0.5 MHz和2.5 MHz正弦相加信號,幅度均為15。然后用QuartusII中lpm_rom模塊得到濾波器輸入數據,再用QuartusII對系統模塊進行仿真,將仿真波形*.vwf文件另存為*.tbl文件,系統模塊仿真波形如圖3所示,最后用Matlab讀取該文件中的數據,得到采樣信號時域波形與頻譜。

6 結束語

采用改進并行DA算法設計了一個16抽頭FIR數字低通濾波器,與全并行DA算法相比,減少了LUT的個數,同時引入倍頻模塊兼顧了運算速度。仿真結果表明,設計系統性能穩定、濾波效果良好、實用性較強。同時,利用改進并行DA算法設計的FIR數字低通濾波器,其系統速度得到大幅提高,由于省去乘法器的使用,減少了LUT的個數,邏輯單元的消耗量也大幅降低。該模塊可以作為其他設計的子模塊,也可用于設計更高階數的濾波器。

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

低通濾波器相關文章:低通濾波器原理

電源濾波器相關文章:電源濾波器原理

晶振相關文章:晶振原理 數字濾波器相關文章:數字濾波器原理

評論