為何Zynq SoC平臺可以使企業的產品利潤激增(二)

平臺:實現盈利衍生品的最佳戰略

本文引用地址:http://cqxgywz.com/article/263142.htm面對不斷增加的研發成本、日漸激烈的競爭以及消費者對更好產品日益苛刻的需求,越來越多的半導體公司和電子產品系統公司開始轉向尋求平臺戰略來快速創建衍生產品并最大限度提高盈利性。平臺戰略能夠進一步降低產品開發時間、加速上市進程并節省工程時間成本,同時能夠提高各種衍生產品或新一代產品的盈利性。

正如IBS研究所顯示,企業通過開發衍生設計“優化收入和利潤”。而采用平臺方法在相同節點開發多種衍生產品(也就是說,衍生產品的衍生產品)使企業能夠進一步優化收入與利潤,因為各個后續設計都能受益于在之前設計中學到的經驗教訓、重新利用以及對客戶需求更準確的了解。

處理選擇是平臺成功的關鍵

企業在實施平臺戰略時做出的兩項最重要的業務決策實際上是關鍵技術決策:眾多處理系統中哪一個會成為產品平臺的核心?該處理系統的哪種芯片實施方案最適合提高盈利性?

在平臺戰略中,處理系統必須滿足或者超過應用軟件和系統需求。它必須具備可擴展性并且易于擴展;必須具有不斷增長的大型成熟生態系統;而且必須允許設計人員和工程師利用之前的設計成果。最后,它必須來自具有發展規劃且成熟穩定的供應商,而且該供應商并未持有偏離其發展規劃或者不斷推出無盡勘誤的不良記錄。雖然有一些候選產品符合上述某些要求,但是能夠滿足或超過全部上述要求的系統是ARM微處理器架構。

|

|

生命周期收入* (百萬美元) |

研發支出(百萬美元) |

生命周期凈利潤** (百萬美元) |

凈現值*** (百萬美元) |

盈利能力指數 |

|

初始復雜ASIC |

$1300 |

$130 |

$260 |

$12.85 |

0.1 |

|

1號衍生品 (80%市場規模) |

$1040 |

$35 |

$208 |

$74.78 |

2.14 |

|

2號衍生品(80%市場規模) |

$650 |

$35 |

$130 |

$34.47 |

0.98 |

* 假設7年。

** 假設利潤率為20%。

*** 假設貼現率為15%。

表1 – 開發衍生設計具有可觀的凈現值(NPV)和更加出色的盈利性指數。

ARM已經成為PC之外一切設備的事實標準嵌入式架構。如今采用高級嵌入式處理技術的絕大部分電子系統——從手機、汽車到醫療設備——都采用ARM處理器內核。尤其是ARM的Cortex-A9處理器架構成為許多種片上系統(SoC)的核心。其不僅已用于專門針對前言智能手機、平板電腦等高量產增值產品開發的ASIC設計中,而且還用于眾多ASSP設計,該設計主要針對那些希望進軍由于缺乏功能差異化而主要展開價格競爭的中小規模成熟市場的公司而開發。

為了增強產品差異化,許多企業基于ARM處理系統創建了將FPGA與現成ASSP融為一體的產品平臺。他們可以在這種配置中實現硬件與軟件細分,從而創造更廣泛的特性組合或者靈活、可升級、性能更高的終端產品——其可幫助他們戰勝那些提供仿效式僅可軟件編程的ASSP實施方案的競爭對手。在這些ASSP中添加賽靈思FPGA已經幫助眾多企業的產品在市場中脫穎而出。

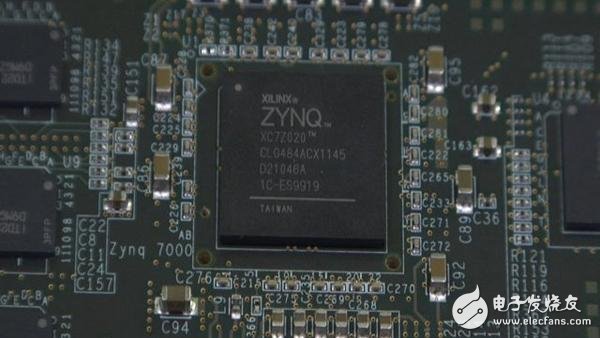

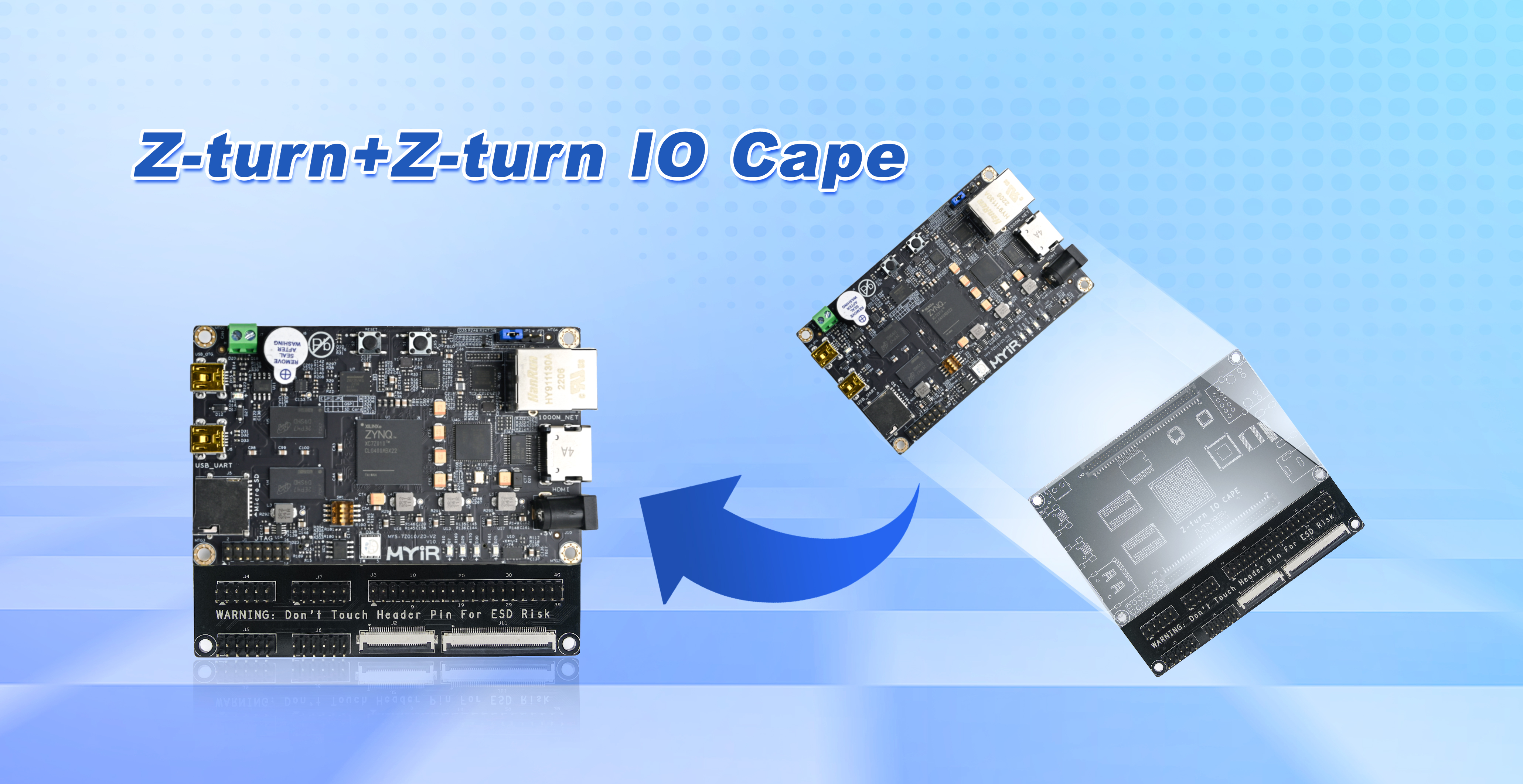

理想平臺解決方案:ZYNQ SoC

借助Zynq-7000 All Programmable SoC,賽靈思正在實施適合絕大部分嵌入式應用的高穩健性ARM Cortex- A9平臺解決方案。如表2所示,作為一種芯片平臺,Zynq SoC具備超過ASIC、ASSP以及ASSP+FPGA組合的眾多優勢。與ARM處理系統的其他硬件實施方案相比,Zynq SoC不僅在NRE、靈活性、差異化、生產力/上市進程等方面具有最佳特性組合,而且還具有最低衍生品成本和最低整體風險(表3)。

另外,Zynq-SoC與其他平臺實施方案相比具有巨大的成本優勢。讓我們來看一下具體數據。

賽靈思 All Programmable SoC產品營銷與管理總監Barrie Mullins表示,設計28nmASIC的平均成本是1.3億美元,而ASIC設計項目的10倍收入目標則為13億美元。他指出,但是,基于Zynq SoC的典型設計項目本質上其整體設計成本比ASIC實施方案低得多而且上市進程也比其快。其原因是Zynq SoC能夠提供預設計、特征化、業經測試與驗證的成品SoC,其可以帶來軟件、硬件、I/O性能以及差異化靈活性。此外,Zynq SoC還受益于低成本且高度集成的賽靈思硬件與軟件設計工具,而ASIC工具流程不但復雜,而且具有嚴重的互操作性及兼容性問題,同時還需要支付高達數百萬的許可費用。設計人員采用賽靈思推薦的UltraFast™方法時賽靈思的設計流程會尤為優化。Mullins補充到,由于賽靈思生態系統IP已經完成設計和預驗證并且賽靈思工具可以生成中間件,因此IP認證成本較低。

|

|

系統總成本 |

靈活性 |

差異化 |

上市進程 |

衍生品成本 |

風險 |

|

Zynq SoC |

低+最高價值 |

最靈活:硬件與軟件可編程性 + 可編程I/O |

可編程性最高,硬件/軟件協同設計 |

集成硬件與軟件差異化速度最快 |

硬件與軟件可編程性帶來最低成本 |

可預測的低風險 |

|

ASSP + FPGA |

高于Zynq SoC (與系統相關) |

非常靈活,但是與Zynq SoC相比ASSP I/O有局限性 |

硬件與軟件可編程性取決于ASSP |

如果ASSP需要硬件細分,則速度最快 |

中低成本,取決于FPGA廠商 |

中低風險,取決于FPGA廠商 |

|

ASSP |

如果只需純軟件可編程性,則最低 |

良好靈活性,但是僅具備軟件可編程性 |

僅具備軟件可編程性 – 便于克隆 |

如果僅需純軟件細分,則速度最快 |

如果需要純軟件衍生品,則成本最低 |

如果僅需純軟件可編程性,則有可能風險最低 |

|

ASIC |

極高,以致無法承擔。 |

制成后僅具備有限軟件靈活性 |

最佳硬件細分,但是軟件細分有局限性 |

速度最低且風險最高 |

最高 |

極高(重新設計) |

最佳平臺特性

良好平臺特性

一般平臺特性

最差平臺特性

表2 – Zynq-7000 All Programmable SoC可為尋求實施平臺戰略的客戶提供理想的特性組合。

|

最低NRE與最佳風險降低 |

最高靈活性與差異化 |

更高生產力與更快上市進程 |

最低衍生品成本與最高盈利性 |

|

√ 成品芯片 √ 開發與設計工具成本微不足道 √ 賽靈思IP庫 + 第三方IP √ 廣泛的開發板 |

√ All Programmable 硬件、軟件與I/O √ 具備隨時現場可編程性 √ 部分重新配置 √ 安全的系統(加密) |

√ 即時硬件/軟件協同開發 √ All Programmable 抽象(C、C++、OpenCV、OpenCL、HDL、基于模型的輸入) √ Vivado Design Suite、Vivado HLS、IP Integrator 與 UltraFast方法 √ 廣泛、開放的OS與IDE支持(開源Linux及Android、FreeRTOS、Windows Embedded、Wind River、Green Hills等) |

√ 基于ARM AMBA AXI4實現IP標準化 √ 重新利用預驗證代碼(ISO、FCC等) √ 重新利用和優化代碼與測試文件 √ 量產芯片、電源電路、PCB與IP許可授權。 |

表3 – 低NRE費用、靈活性等要素使Zynq SoC成為平臺戰略的理想選擇。

Mullins指出,因此典型Zynq SoC項目需要2300萬美元。由此實現設計項目的標準10倍收入目標需要生命周期收入達到2.3億美元——此10倍目標比實現ASIC實施方案所需達到的13億美元10倍目標更易于實現,而且也更可行(表4)。

采用的上述方法分析IBS數據時,如果我們假設在Zynq SoC 中實現的初始復雜設計能夠完全占領同樣的13億美元目標市場,則利用57名工程師只需要2300萬美元就能夠在兩年內完成產品。

如果假設初始Zynq SoC設計具有與初始ASIC設計相同的20%利潤率,則初始Zynq SoC設計的NPV為1.0727億美元,而PI為3.7,其明顯優于初始ASIC的1285萬美元NPV和僅有0.1的PI。利潤率同樣為20%的Zynq SoC的NPV與PI更加可觀(表5)。

|

|

28nmASIC(IBS數據) |

|

Zyng SoC (賽靈思估算) |

|||

|

% |

大概工程月數 |

總成本(百萬美元) |

% |

大概工程月數 |

總成本(百萬美元) |

|

|

硬件 |

|

|

|

|

|

|

|

IP認證 |

26 |

704 |

11.8 |

20 |

240 |

4.0 |

|

架構 |

8 |

209 |

4.2 |

45 |

100 |

2.1 |

|

驗證 |

53 |

1431 |

28.9 |

35 |

160 |

3.0 |

|

物理設計 |

13 |

350 |

6.9 |

0 |

0 |

0 |

|

硬件小計(設計工程資源) |

100 |

2694 |

51.8 |

100 |

500 |

9.1 |

|

軟件 |

|

4296 |

59.8 |

|

720 |

10.0 |

|

原型成本(百萬美元) |

2.1 |

1.0 |

||||

|

原型驗證 |

|

815 |

16.6 |

|

140 |

2.8 |

|

總計 |

|

7805 |

130.3 |

|

1360 |

22.9 |

c++相關文章:c++教程

評論