解析FPGA低功耗設計

下面介紹一下優化BRAM功耗的方法:

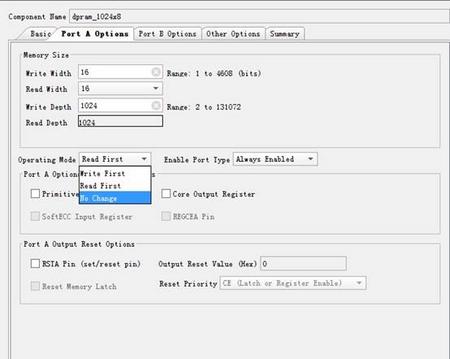

本文引用地址:http://cqxgywz.com/article/264714.htma)使用“NO CHANGE”模式:在BRAM配置成True Dual Port時,需要選擇端口的操作模式:“Write First”,“Read First” or “NO CHANGE”,避免讀操作和寫操作產生沖突,如圖6所示;其中“NO CHANGE”表示BRAM不添加額外的邏輯防止讀寫沖突,因此能減少功耗,但是設計者需要保證程序運行時不會發生讀寫沖突。

圖6

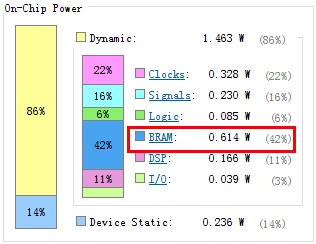

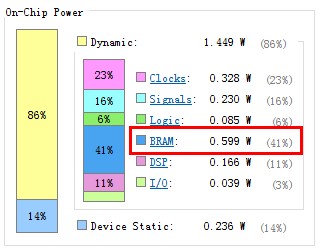

圖5中的功耗是設置成“Write First”時的,圖7中是設置成“NO CHANGE”后的功耗,BRAM的功耗從0.614W降到了0.599W,因為只使用了7%的BRAM,如果設計中使用了大量的BRAM,效果能更加明顯。

圖7

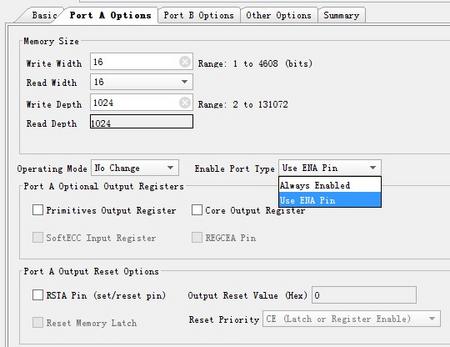

b)控制“EN”信號:BRAM的端口中有clock enable信號,如圖8所示,在端口設置中可以將其使能,模塊例化時將其與讀/寫信號連接在一起,如此優化可以使BRAM在沒有讀/寫操作時停止工作,節省不必要的功耗。

圖8

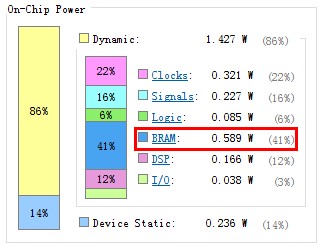

如圖9所示為控制“EN”信號優化后的功耗情況,BRAM功耗降到了0.589W。

圖9

c)拼深度:當設計中使用了大量的存儲器時,需要多塊BRAM拼接而成,如需要深度32K,寬度32-bit,32K*32Bit的存儲量,但是單塊BRAM如何配置是個問題?7 series FPGA中是36Kb 的BRAM,其中一般使用32Kb容量,因此可以配置成32K*1-bit或者1K*32-bit,多塊BRAM拼接時,前者是“拼寬度”(見圖10),后者是“拼深度”(見圖11)。兩種結構在工作時,“拼寬度”結構所有的BRAM需要同時進行讀寫操作;而“拼深度”結構只需要其中一塊BRAM進行讀寫,因此在需要低功耗的情況下采用“拼深度”結構。

注:“拼深度”結構需要額外的數據選擇邏輯,增加了邏輯層數,為了降低功耗即犧牲了面積又犧牲了性能。

圖10

圖11

fpga相關文章:fpga是什么

評論