基于FPGA的LCD顯示遠程更新的設計方案及原理圖

Nexys3基本系統生成器(BSB)支持包自動生成一個測試應用程序的以太網MAC。ISE的設計可以使用IP內核發生器用向導來創建一個以太網MAC控制器IP核。如果COL此信號置位時表示碰撞條件的檢測MLL模式。在MLL模式中:

本文引用地址:http://cqxgywz.com/article/266573.htm1.傳輸數據時的控制信號為TXCLK,當TXCLK為上升沿時控制器同步傳輸數據,TXEN為高電平時表明此時控制器傳輸的數據是有效的,若TXER為高電平時,說明傳輸檢測到錯誤。

2.接受數據時,在RXCLK為上升沿時RXD[3:0]開始接受數據。控制信號RXCLK為上升沿接收數據時,接受信號RXDV為高電平。如果RXER為高電平時說接受檢測到錯誤。

MDIO信號是表明串行管理接口的數據輸入/輸出,MDC是串行管理接口的時鐘信號

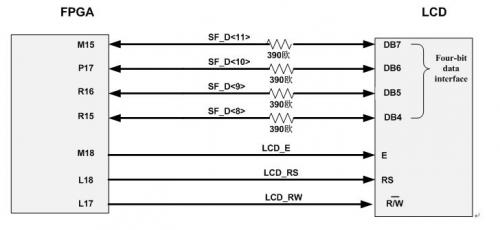

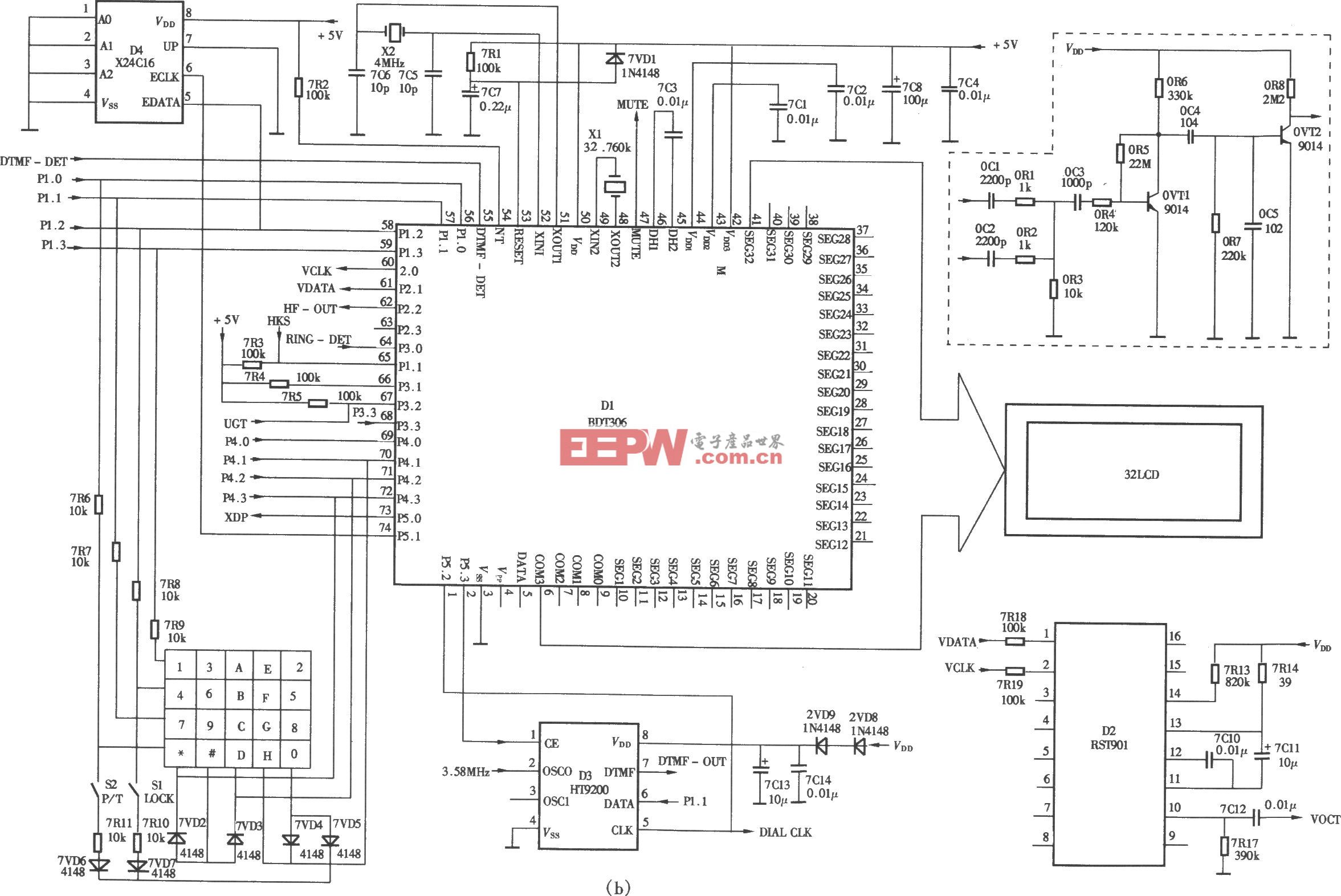

(3) LCD模塊的結構圖

圖5 LCD模塊結構圖

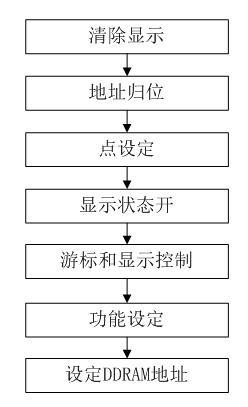

為盡可能減少針腳數從而達到管腳復用的目的,FPGA通過四位數據線接口控制LCD,由于在初始化之后,所有的數據和命令都以8位傳送,故每8位命令被分成2個四位即高4位和低4位,先傳高4位,后傳低4位,其間間隔只是1us。數據線上的四個390Ω電阻是用來防止管腳超載起到保護的作用。下圖是LCD的初始化流程圖

圖4 LCD初始化流程圖

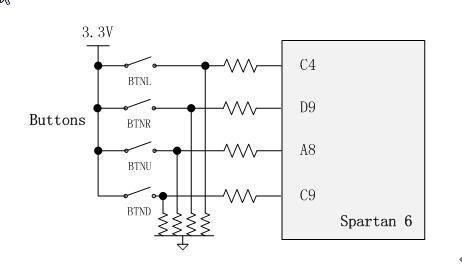

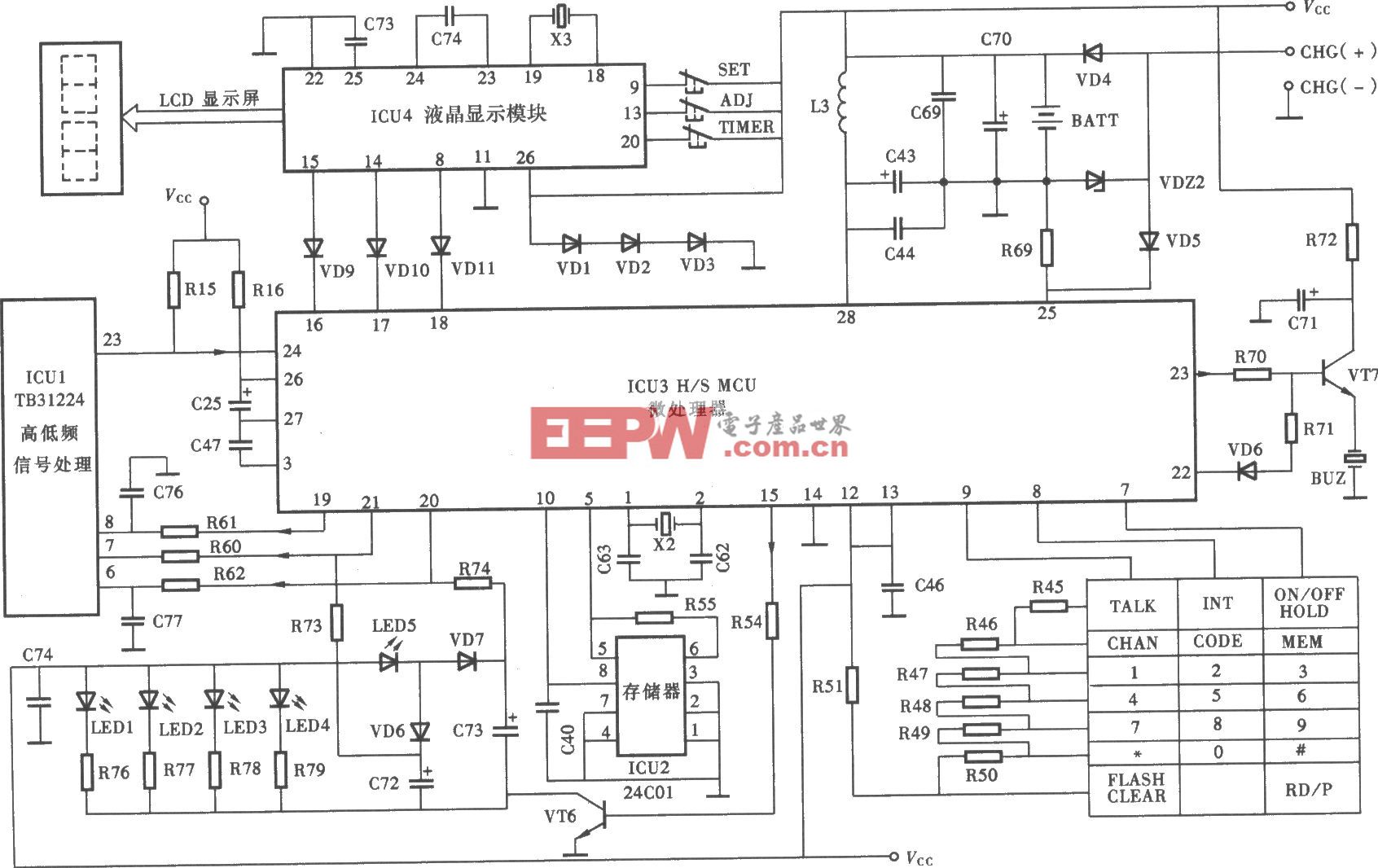

(5)按鍵模塊

圖6 按鍵模塊圖

系統完成初始化后,Spartan-6 FPGA的C4,D9,A8,C9管腳都是低電平,當有一個按鍵按下時,對應的管腳會變成3.3V高電平,按鍵掃描程序檢測出高電平后跳轉到相應的中斷地址,執行中斷程序。

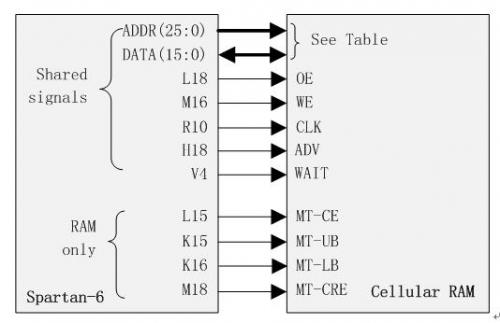

(6)存儲器模塊

圖7 存儲器模塊

本設計使用Nexys3 SPARTAN6開發板上的存儲資源Cellular RAM 作為存儲器,采用同步模式進行傳輸,時鐘信號CLK低電平時有效。 在讀模式時,寫使能引腳WE為高電平,ADV,CRE,CE,OE,LB,UB為低電平,地址信號從ADDR[25:0]輸入,保存的數據從DQ[15:0]輸出;在寫模式時,WE,ADV,CRE,CE,LB,UB為低電平狀態,OE可以為任何狀態。地址信號從ADDR[25:0]輸入,需要存儲的數據從DQ[15:0]端輸入。

LCD顯示屏相關文章:lcd顯示屏原理

lcd相關文章:lcd原理

評論