基于FPGA的LCD大屏幕拼接系統的設計

3.2.3 水平與垂直插值單元

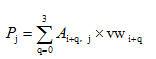

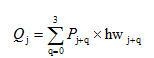

本文引用地址:http://cqxgywz.com/article/266848.htm根據公式(7)和(8),水平與垂直插值有同樣的運算,但是它們是并行執行以提高整體的速度。水平與垂直插值的邏輯結構由圖5所示,乘法器與加法器可以有效的完成輸入的數據的卷積與拼配相應的4個加權系數來產生插值的電路。

水平插值單元 垂直插值單元

圖5水平與垂直插值單元邏輯框圖

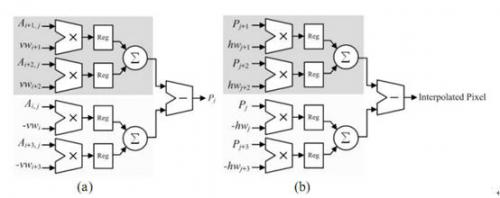

3.2.4虛擬像素緩存器

虛擬像素點是由垂直插值產生并存于虛擬像素緩存器中,在水平插值的過程被調用。一般來說,縮放比例會決定這緩存器輸入與輸出數據的速率,當放大的時候,每個虛擬像素會被重新用于水平插值以致于垂直插入器數據速率會比水平的要低,相反的,在縮小的時候,虛擬像素由垂直插值過程產生的會比水平插值過程所需求的要多。為了調節不同的數據速率,設計虛擬像素緩存器如圖6所示,其中包含1個計數器,8個寄存器和緩存輸出控制電路。在插值放大的過程中,緩存器有時會延緩垂直插值,虛擬像素數量比水平插值所需求的確定數量要多的時候,就會停止虛擬像素的產生。計數器則是記錄著最新產生的虛擬像素點的列地址并存于reg7.比較器和選擇器對比計數器和

圖6 虛擬像素緩存器

4、驗證

算法的驗證是基于Xilinx Virtex-4 FPGA開發平臺,對視頻分割模塊及延展式線性插值模塊分別進行仿真,驗證算法的正確性,再經反復的優化及測試,最后下載到開發板,驗證輸出的視頻顯示效果是否能夠滿足視頻放大的應用需求,完成LCD大屏幕拼接系統的設計。

LCD顯示屏相關文章:lcd顯示屏原理

lcd相關文章:lcd原理

評論