基于FPGA 的FIR 數字濾波器設計方案

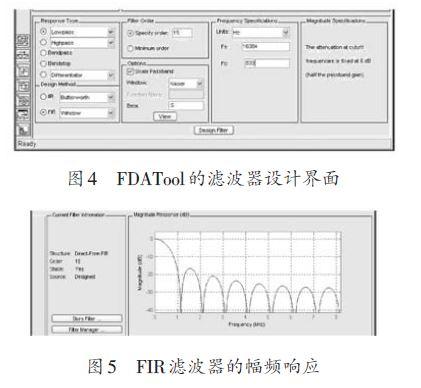

模型搭建好之后,需要確定16階FIR數字濾波器的系數,在這使用Matlab中的FDATool濾波器設計工具來確定。確定好濾波器的指標:

本文引用地址:http://cqxgywz.com/article/267746.htm(1)設計一個16階的FIR濾波器;

(2)低通濾波器;

(3)采樣頻率fs為16 384 Hz,截頻點頻率fs為533 Hz;

(4)輸入序列位寬為16位。

在設計濾波器界面中,如圖4所示,進行下列選擇:

(1)濾波器類型(Filter Type)為低通(Lowpass);

(2)設計方法(Design Method)為FIR,采用窗口法(Window);

(3)濾波器階數(Filter Order)定制為15(設置為15階而不是16階,是由于設計的16階FIR濾波器的常系數項h(0)=0);

(4)濾波器窗口類型為Kaiser,Beta為0.5.

所有的選項確定好后,在FDATool濾波器設計界面中點擊“Design Filter”,Matlab就會計算濾波器系數并作相關分析。圖5所示為濾波器的幅頻響應,圖6所示為濾波器的階躍響應。

由于所有的模塊都在同一個Simulink圖中,這時的Simulink設計圖顯得很復雜,不利于閱讀和排錯,因此把FIR數字濾波器模型做成一個子系統在設計圖中顯示出來,如圖7所示,這就是Matlab中的層次化設計,在頂層設計圖中,濾波器作為名稱是SubFIR_533_16js的一個模塊出現。同時,圖7中還設置了其他模塊,包括仿真信號輸入模塊、Signal TapⅡ信號實時監測模塊、Signal Compiler模塊、硬件開發板模塊、TestBench模塊。

這樣整個濾波器的Simulink電路設計模型就完成了,然后要對該模型進行系統級仿真,查看其仿真結果,在頻率為533 Hz的波形輸入上加入了頻率為3 600 Hz的擾動波形,其Simulink仿真結果如圖8所示。

圖中,上面的波形是533 Hz的輸出,中間的波形是533 Hz加上3 600 Hz高頻干擾后的輸出,下面的波形是經過濾波后的輸出。

3.2從模型文件到Verilog代碼的RTL級轉換和編譯適配

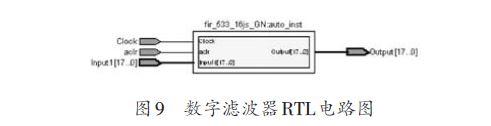

利用Signal Compiler模塊將電路模型文件即Simu-link模塊文件(。mdl)轉換成RTL級的Verilog代碼表述和Tcl(工具命令語言)腳本。這種轉換是用來對數字濾波器Simulink模型進行結構化分析的[5].獲得轉換好的VHDL描述后就可以調用Verilog綜合器,這里我們選用QuartusⅡ,用來生成底層網表文件,同時也就可以得到其網表文件對應的RTL電路圖。如圖9所示。

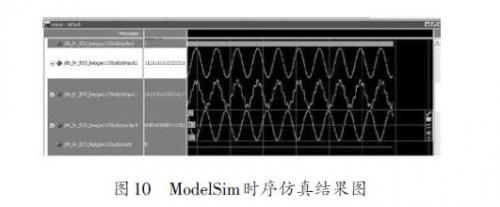

3.3數字濾波器的ModelSim功能仿真

ModelSim軟件可支持VHDL和Verilog混合仿真,無論是FPGA設計的RTL級和門級電路仿真,還是系統的功能仿真都可以用ModelSim來實現[4-5].由Signal Com-piler生成的Verilog硬件描述語言模塊,在ModelSim中可以直接對Verilog代碼進行仿真,檢測源代碼是否符合功能要求。圖10所示的16階FIR數字濾波器的功能仿真結果圖。與圖8的Simulink仿真結果圖的波形一致,表明經過轉換的Verilog源代碼可以實現正常的濾波功能。

3.4 FIR數字濾波器的FPGA硬件實現

FIR數字濾波器一般是嵌入在采集器的采集板卡中進行工作的,把由數字濾波器的Verilog源代碼生成的模塊嵌入到采集板卡的FPGA邏輯中,如圖11所示。

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

數字濾波器相關文章:數字濾波器原理

評論