詳解TINY6410硬件電路設計之二

—— 解密SDRAM電路

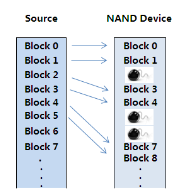

書接上回, CPU,NANDFLASH和SDRAM是嵌入式系統中最重要的三個組成部分。作為嵌入式系統的神經元NANDFLASH,上回得到了充分的分析,不知道你還有印象沒有。這次我們來分析下友善的TINY6410的心臟--SDRAM部分。之所以說其為嵌入式系統的心臟,是因為嵌入式系統在運行過程中,操作系統、應用程序等都在其中。如果沒有該部分,嵌入式系統可以裸機運行,這樣就失去了嵌入式系統的優勢。

本文引用地址:http://cqxgywz.com/article/268241.htmS3C6410支持兩個DRAM片選,可以分別最大接256MB的內存。片內 DRAM控制器是來自ARM的PrimeCell Dynamic Memory Controller(PL340)。因此要想真正搞明白SDRAM,需要查看6410的數據手冊和PL340的數據手冊。

首先來看下該板子SDRAM的數據手冊K4X1G163PE:

從中可以得到三個信息:大小64MB,16位和1.8V工作電壓

。

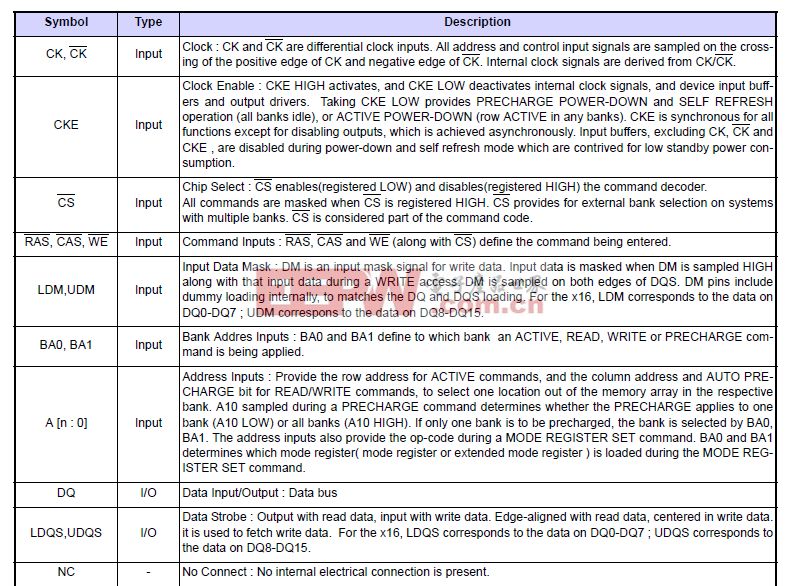

然后看該內存的關鍵管腳描述:

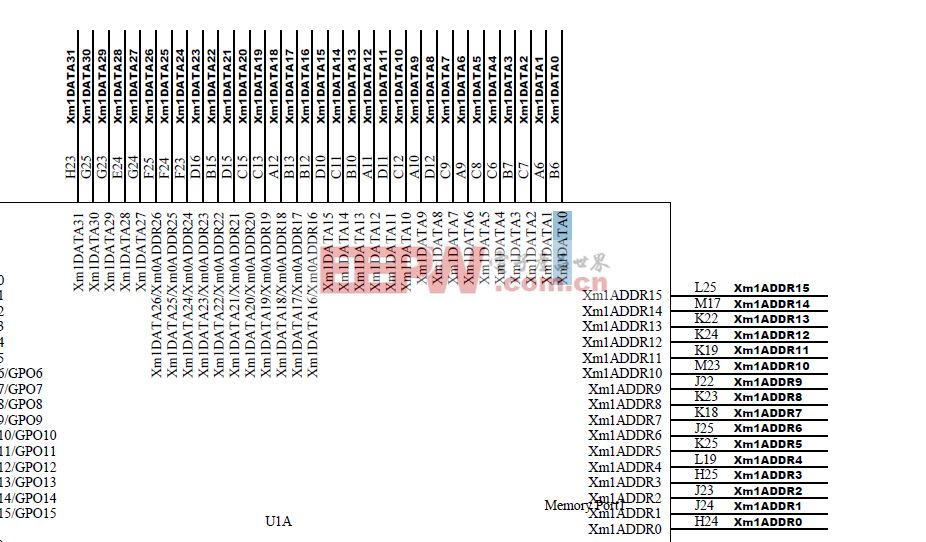

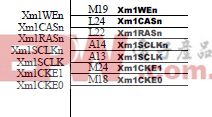

從表中可以看出內存需要的一些管腳:時鐘、時鐘使能、行列地址和寫使能、輸入屏蔽位、快選擇位、地址線、數據線、數據存儲控制器和電源。知道這些后來看下K4X1G163PE和CPU6410的硬件連接如下:

![]()

S3C 6410核心板SDRAM接口

電路相關文章:電路分析基礎

晶振相關文章:晶振原理

評論