跨越鴻溝:同步世界中的異步信號

現在指針邏輯的設計有多種方法。第一種方法是將讀、寫選通進行同步,同時在各個時鐘域使用計數器來跟蹤 FIFO 中可用的項。計數器反映出可用于讀寫的 FIFO 項目號,計數器也與相應的端口同步。讀計數器跟蹤包含有效數據的項數,而寫計數器則跟蹤可以存儲數據的項數。當對指針邏輯進行復位時,由于沒有數據可讀,讀計數器從零起始。寫計數器則從 FIFO 中項的總數開始計數,即所有項均可用來存儲數據。

本文引用地址:http://cqxgywz.com/article/268638.htm讀選通信號累減讀計數器,并與寫時鐘域同步,因為它同時也累加寫計數器。寫選通信號則累減寫計數器,并與讀時鐘域同步,因為它同時也累加讀計數器。

這種設計需要單時鐘寬度脈沖以及用于讀、寫選通的脈沖同步器,因為當一個電平信號從一個時鐘域跨越到

另一個更快的時鐘域時,在較快時鐘域中它能在更多的時鐘周期中保持有效。由于只要讀或寫信號是有效的,每個計數器就會發生變化,因此較快的時鐘域就檢測到更多的讀、寫,超出較慢時鐘域實際發生的數量。脈沖同步器可以將一個時鐘域的時鐘寬度脈沖轉換為新時鐘域的時鐘寬度脈沖,每個脈沖都表示一次 FIFO 的讀或寫。

這種 FIFO 狀態技術對讀、寫狀態都不太有利。當 FIFO 中所有項均充滿時,寫端口狀態指示為滿,并在讀選通觸發后繼續指示 FIFO 滿,因為同步過程會使選通信號延遲送給寫計數器。讀端口為空時也會出現這種情況,因為同步過程會使寫選通信號延遲到達讀計數器。

這種設計的另一種考慮是及時檢測全滿/全空狀態。如果 FIFO 還有一項可用,并且有寫選通觸發,則 FIFO 必須立即置為全滿狀態。這樣才能提前一個時鐘給出全滿標志,使 FIFO 有足夠時間防止下一個數據寫入而產生溢出。對 FIFO 的讀端口也是這樣。這種情況下,如果 FIFO 里只有一個數,并且有讀選通觸發,則必須置全空狀態,以給讀電路足夠的時間防止讀空 FIFO。

這種指針邏輯限制電路在每個時鐘周期中訪問 FIFO,即使在慢速時鐘域中也是這樣。這一功能的優點在于訪問 FIFO 的電路至少有一個時鐘周期來評估 FIFO 的狀態。FIFO 可以將所有項都填滿數據,而不會出現數據被覆蓋或全空無數據可讀的情況。這種設計的另一個優點是每一端都可以讀其相應的計數器,來判斷 FIFO 中還有多少項可用。設計者可以將這種 FIFO設計用在進行多次數據讀/寫的電路中,而不會造成上溢或下溢的情況。

這種設計的不足之處是由計數器來判斷狀態,而不是直接比較讀、寫指針。對大型 FIFO 來說,這些計數器也很大。而且,由于使用脈沖同步時,來自較快時鐘域的讀、寫脈沖在較慢時鐘域的脈沖間至少必須有兩個時鐘周期,因此平均數據速率為最低時鐘頻率的一半。解決這些問題的一種方法是采用直接指針比較法。

在這種 FIFO 設計中,讀、寫指針的比較決定了 FIFO 的狀態。異步設計中的指針比較更富有挑戰性,因為每個指針位于不同的時鐘域中,對信號總線的同步要求在同步握手信號期間總線不發生改變。將這種技術用于指針同步的 FIFO 設計可能會很慢。要解決這個問題,FIFO 指針邏輯使用了格雷碼,代替指針使用的二進制碼。

格雷碼在每一次計數增減時只改變其中的一位(表 3)。你可以在格雷碼總線上使用同步器,因為每一次總線改變時只有一根信號線有變化,于是就消除了格雷碼總線各位通過不同同步器時的競爭情況。這種設計的指針為格雷碼計數器。使用二進制指針時需要將其變換成格雷碼后的同步指針,而使用變換邏輯會違反對同步信號的限制,即同步的信號在跨越時鐘域前要來自觸發器。

表 3

格雷碼計數器是一個二進制累加器,在累加器前、后各帶有一個轉換器,分別用于格雷碼轉換為二進制碼,和二進制碼轉換為格雷碼(圖 8)。格雷碼與二進制碼的轉換是一個異或運算,所以只需比一個二進制計數器多幾個邏輯電平。在格雷碼轉換成二進制碼時,使用:BN=GN;BN-1=BN+GN-1;BN-2=BN-1+GN-2 . B1=B2+G1;B0=B1+G0。而將二進制碼轉換成格雷碼時,使用:GN=BN;GN-1=BN+BN-1;GN-2=BN-1+BN-2 . G1=B2+B1;G0=B1+B0。在設計中可以采用同樣的技術來比較格雷碼指針的值,即在各個指針與二進制比較邏輯之間增加轉換器。

圖8,格雷碼計數器是一個二進制累加器,在累加器前、后各帶有一個轉換器。

用這種指針邏輯的 FIFO 很快,每個時鐘周期中電路都可以讀寫 FIFO。但是,在每個周期都訪問 FIFO 意味著 FIFO 狀態要包括“將滿”和“將空”兩種指示,這樣讀寫 FIFO 的電路才能有停止時間。“將滿”表示只能再寫入一項,“將空”則表示只有一項可讀。這種情況描述了一個要求最少的可能狀態信號的設計,以及一個需要更多指示的設計,如果在固定的最小尺寸情況下用猝發方式訪問 FIFO 的電路的話。

這種 FIFO 狀態技術會給讀、寫帶來不良狀態。當 FIFO 滿時,寫端口的狀態指示已滿,而在電路從 FIFO 中讀出一項后,該狀態仍為滿,因為同步機制使讀指針相對寫入一側的比較邏輯有個延遲。同樣,在讀出一側的空狀態指示也有這個問題,因為同步機制使寫指針相對讀出一側的比較邏輯有延遲。

如果你在設計跨不同時鐘域電路時,使用一些技術來降低通信失敗的風險,則處理跨時鐘域的信號就不再是艱巨的任務。同步機制可以防止接收跨時鐘域信號的觸發器出現亞穩態,從而避免導致不可預知的電路行為。對于在多個時鐘周期內一直保持有效的信號來說,電平同步器的效果很好。對于要轉換成新時鐘域脈沖的較慢時鐘域電平信號,要采用邊沿檢測同步器。最后,對跨時鐘

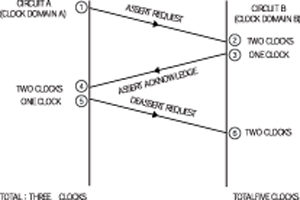

域的脈沖信號應使用脈沖同步器。還要記住,當一個信號總線跨越時鐘域時,整個總線要在同一個時鐘周期內到達新的時鐘域。不要分別同步每一個信號,而要采用一個保持寄存器和握手方式。握手用來表示寄存器中的信號何時有效,何時可以采樣。對數據總線來說,握手和一個保持寄存器很有用,但每次向新時鐘域傳送的數據字不超過一個。

模擬信號相關文章:什么是模擬信號

電路相關文章:電路分析基礎

脈沖點火器相關文章:脈沖點火器原理

評論