Berkeley Design:IC設計需要高效軟件

——

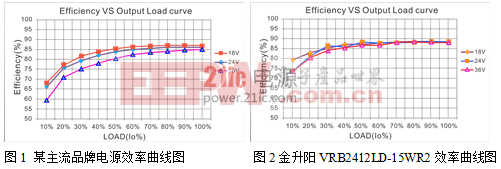

數字技術在電子產品中得到了廣闊的應用,數字技術的發展帶來的結果不是模擬技術的減少而是增加。數字采用的不過是新的技術,而模擬采用的則是全部的技術,現在模擬技術采用的技術已經幾乎與數字完全相同。消費電子的發展有兩大趨勢,一是內存的增加速度越來越快,另一個是模擬電源技術的增多,供電量增加電源管理難度也隨之加大。不僅如此,模擬和RF電路在半導體元件中變得越來越普及,復雜時鐘和IO也更加重要,模擬IP則是隨處可見。因此,如何應對模擬電路快速在IC中增加是個問題,解決這個問題更多的依靠軟件的支持。

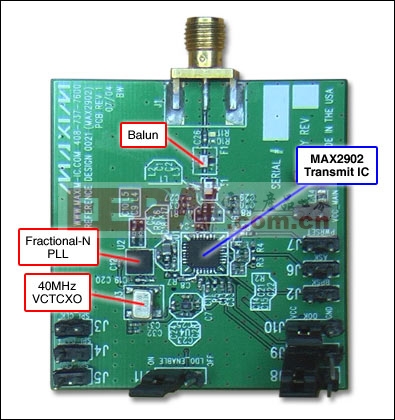

目前,對模擬電路分析主要采用傳統的SPICE,而對數字電路則流行Digital FastSPICE,但兩種方法都存在很難同時高速且高效地同時支持數字和模擬信號分析的尷尬。正是看到這樣一個局勢,Berkeley Design開發出Precision Circuit Analysis軟件,實現對模擬和數字混合信號的高速與高效分析,可以有效地將仿真時間縮短到原來的1/10甚至更短。該軟件包括Analog FastSPICE、RF FastSPICE和PLL Noise Analyzer等功能,適合于絕大多數混合信號的仿真與開發分析。該類軟件特別適合消費電子、電信與網絡應用,目前已經可以支持45nm芯片設計。正如該公司CEO所說:“我們的工具縮短了電路驗證與芯片測定之間不斷增加的差別。”

評論