利用Allegro實現嵌入式系統高速電路布線設計

1.在Allegr o的assign diff pair菜單中選擇建立差分對的信號Tx+/-,命名為TX_Pair。

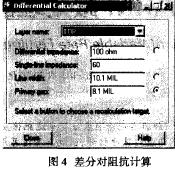

本文引用地址:http://cqxgywz.com/article/85065.htm2.按照對信號TX+/-阻抗控制要求計算差分對線寬、線距,如圖4所示,選擇走線層面top層,填入差分對阻抗100歐,單線阻抗60歐,得到線寬10.1mil,主要線間距8.1mil。

3.定義差分對TX_PAIR電氣約束條件:

主要線寬,線間距:10mil/8mil;

次要線寬/線間距:10mil/8mi;

線最小間距:6mil;

兩條線無法走到一起時允許的線長:100mil;

兩條線可允許的誤差值:25mil。

4.分配差分對TX_PAIR到電氣約束集,打開差分對DRC模式。

圖4差分對阻抗計算

以上實現差分對走線和阻抗控制的方法在涉及到大量差分對的通信系統電路中非常簡單實用。

4 結語

筆者利用強大的PCB設計軟件Allegro實現了基于EP9315嵌入式系統的硬件電路設計。該板采用6層PCB布線,完全滿足高速電路設計中對等長、差分、阻抗控制的要求。 基于該電路設計的嵌入式系統與武漢中科院巖土力學所設計的SY5聲波工程檢測儀實現了良好接口,與由51單片機搭建的原 SY5 聲波儀相比,改系統功耗降低,體積變小,穩定性增強,成本降低,更適合工業控制中的運用。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)DIY機械鍵盤相關社區:機械鍵盤DIY

評論