基于LEON3處理器和Speed協處理器的復雜SoC設計實現*

利用AHB實現通信

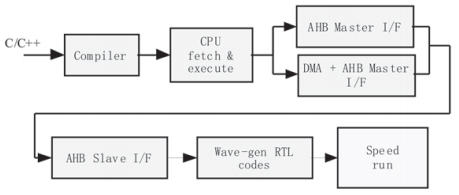

本文引用地址:http://cqxgywz.com/article/94563.htm為了實現可編程,需要將C/C++程序表達的信息經過編譯器、LEON3處理器、AHB總線、DMA控制器和必要的HDL代碼,轉化成Speed能夠識別的信息,進入Speed模塊中,如圖2。其中AHB總線是LEON3 Core和Speed Core結合的關鍵。

圖2 實現軟件可編程的過程

AHB總線及AHB控制器

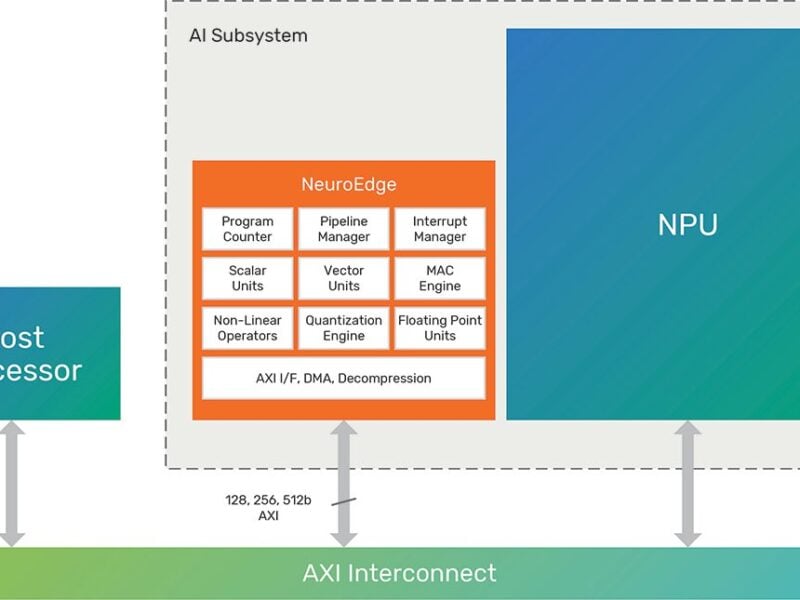

AMBA總線是一種應用廣泛的層次化總線結構,有高速的AHB和低速APB之分,其中AHB是一種流水式高速總線結構,地址和數據總線相互獨立,可掛載16個Master和Slaver設備,常用來組織和連接高性能模塊,如處理器、DMA控制器、協處理器等[5~7]。AHB總線的核心是AHB控制器,主要包括仲裁器,譯碼器和多路復用器,其中仲裁器選擇AHB Master,而譯碼器選擇AHB Slave,實現寫數據WDATA和讀數據RDATA分開,如圖3所示。

評論