?布線 文章 最新資訊

信號(hào)完整性與制造性PCB設(shè)計(jì)方法

- 在以原理圖形式化電路功能并決定采用的零件、器件和技術(shù)后,下一步是創(chuàng)建功能性的PCB布局。這一步旨在將所有元件安裝在PCB上并建立所有必要的連接,確保板塊尺寸最小,并滿足應(yīng)用特定目標(biāo),如最小損耗或最大信號(hào)完整性。然而,這一過程可能非常復(fù)雜,不僅僅是在電子元件之間繪制連接。本文將介紹在產(chǎn)品生命周期這一關(guān)鍵階段需要牢記的重要最佳實(shí)踐方法。利用子電路實(shí)現(xiàn)元件的最佳布置PCB設(shè)計(jì)中的子電路識(shí)別顯著影響器件的布置和布線策略。通過隔離電路中的特定功能模塊,設(shè)計(jì)師可以戰(zhàn)略性地布置元件,確保PCB空間和短信號(hào)路徑的高效利用

- 關(guān)鍵字: PCB ?布線 通孔 多層PCB

量子元件產(chǎn)業(yè)正在興起

- 量子計(jì)算機(jī)核心的嚴(yán)酷溫度和脆弱的量子態(tài)對(duì)支持它們的電子設(shè)備施加了極大限制。迄今為止,量子計(jì)算公司不得不自行解決這些挑戰(zhàn),但隨著該領(lǐng)域的成熟,一個(gè)新興的量子零部件產(chǎn)業(yè)正在涌現(xiàn),提供現(xiàn)成解決方案。超導(dǎo)量子比特和硅自旋量子比特——兩項(xiàng)最流行的量子計(jì)算技術(shù)——都需要極低溫度才能防止熱噪聲干擾計(jì)算。這意味著它們必須保存在專用稀釋冰箱中,冷卻溫度可降至約20毫利科爾文(-273.13攝氏度)。這些冰箱空間有限,在極低溫度下冷卻能力也非常有限。冷卻功率是設(shè)備在一定時(shí)間內(nèi)能去除多少熱量的指標(biāo),隨著溫度接近絕對(duì)零度,散熱量

- 關(guān)鍵字: 量子元件 量子計(jì)算機(jī) CMOS晶體管 放大器 布線

電源設(shè)計(jì)器件布局和布線要點(diǎn)

- 在電源設(shè)計(jì)中,精心的布局和布線對(duì)于能否實(shí)現(xiàn)出色設(shè)計(jì)至關(guān)重要,要為尺寸、精度、效率留出足夠空間,以避免在生產(chǎn)中出現(xiàn)問題。我們可以利用多年的測(cè)試經(jīng)驗(yàn),以及布局工程師具備的專業(yè)知識(shí),最終完成電路板生產(chǎn)。精心的設(shè)計(jì)的效率設(shè)計(jì)從圖紙上看起來可能毫無問題(也就是說,從原理圖角度),甚至在模擬期間也沒有任何問題,但真正的測(cè)試其實(shí)是在布局、PCB制造,以及通過載入電路實(shí)施原型制作應(yīng)力測(cè)試之后。這部分使用真實(shí)的設(shè)計(jì)示例,介紹一些技巧來幫助避開陷阱。我們將介紹幾個(gè)重要概念,以幫助避開設(shè)計(jì)缺陷和其他陷阱,以免未來需要重新設(shè)計(jì)和

- 關(guān)鍵字: PCB 電源設(shè)計(jì) 布線

PCB設(shè)計(jì)要點(diǎn)總結(jié)

- PCB布線工作對(duì)于很多工程師來講就是連連看,而且還是一項(xiàng)非常枯燥乏味的工作。這其實(shí)只是一個(gè)初級(jí)的認(rèn)知,一位優(yōu)秀的PCB設(shè)計(jì)工程師還是能做很多工作并能解決很多產(chǎn)品設(shè)計(jì)中的問題的。本文結(jié)合一些大廠的設(shè)計(jì)規(guī)則以及部分的技術(shù)文章,將分享一些PCB設(shè)計(jì)中布線的要點(diǎn),僅供參考。1、通用做法在進(jìn)行PCB 設(shè)計(jì)時(shí),為了使高頻、高速、模擬電路板的設(shè)計(jì)更合理,抗干擾性能更好,應(yīng)從以下幾方面考慮:(1)合理選擇層數(shù);在 PCB 設(shè)計(jì)中對(duì)高頻、高速電路板布線時(shí),利用中間內(nèi)層平面作為電源和地線層,可以起到屏蔽的作用,能有效降低寄生

- 關(guān)鍵字: PCB設(shè)計(jì) 布線

為啥網(wǎng)線都會(huì)限制傳輸距離為100米?

- 無論是五類雙絞線,還是六類雙絞線,傳輸距離都是100米。而且,在綜合布線規(guī)范中,水平布線不能超過90米,鏈路總長度不能超過100米。換句話說,“100米”是有線以太網(wǎng)布線的一個(gè)極限。這個(gè)說法到底怎么來的,有啥依據(jù),具體施工現(xiàn)場(chǎng)怎么操作,一篇給你說明白。網(wǎng)線數(shù)據(jù)傳輸最大距離對(duì)網(wǎng)絡(luò)比較了解的網(wǎng)工朋友,都知道雙絞線有一個(gè)“無法逾越”的“100米”傳輸距離。無論是100M傳輸速率的五類雙絞線,還是1000M傳輸速率的六類雙絞線,最遠(yuǎn)有效傳輸距離都為100米。在綜合布線規(guī)范中,也明確要求水平布線不能超過90米,鏈路

- 關(guān)鍵字: 網(wǎng)線 傳輸距離 雙絞線 布線

電路板廠PCB關(guān)鍵信號(hào)如何去布線?

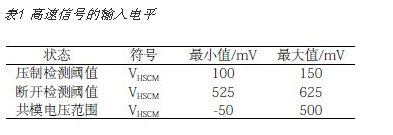

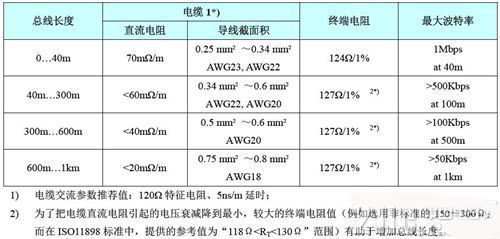

- 電路板廠在PCB布線規(guī)則中,有一條“關(guān)鍵信號(hào)線優(yōu)先”的原則,即電源、摸擬信號(hào)、高速信號(hào)、時(shí)鐘信號(hào)、差分信號(hào)和同步信號(hào)等關(guān)鍵信號(hào)優(yōu)先布線。接下來,我們不妨就來詳細(xì)了解下這些關(guān)鍵信號(hào)的布線要求。模擬信號(hào)布線要求模擬信號(hào)的主要特點(diǎn)是抗干擾性差,布線時(shí)主要考慮對(duì)模擬信號(hào)的保護(hù)。對(duì)模擬信號(hào)的處理主要體現(xiàn)在以下幾點(diǎn):1. 為增加其抗干擾能力,走線要盡量短。2. 部分模擬信號(hào)可以放棄阻抗控制要求,走線可以適當(dāng)加粗。3. 限定布線區(qū)域,盡量在模擬區(qū)域內(nèi)完成布線,遠(yuǎn)離數(shù)字信號(hào)。高速信號(hào)布線要求1. 多層布線據(jù)電路板廠了解,

- 關(guān)鍵字: 電路板 PCB 布線

imec首度展示晶背供電邏輯IC布線方案 推動(dòng)2D/3D IC升級(jí)

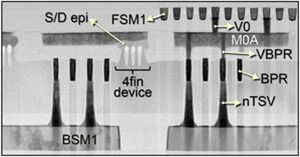

- 比利時(shí)微電子研究中心(imec)于本周舉行的2022年IEEE國際超大規(guī)模集成電路技術(shù)研討會(huì)(VLSI Symposium),首度展示從晶背供電的邏輯IC布線方案,利用奈米硅穿孔(nTSV)結(jié)構(gòu),將晶圓正面的組件連接到埋入式電源軌(buried power rail)上。微縮化的鰭式場(chǎng)效晶體管(FinFET)透過這些埋入式電源軌(BPR)實(shí)現(xiàn)互連,性能不受晶背制程影響。 FinFET微縮組件透過奈米硅穿孔(nTSV)與埋入式電源軌(BPR)連接至晶圓背面,與晶圓正面連接則利用埋入式電源軌、通孔對(duì)

- 關(guān)鍵字: imec 晶背供電 邏輯IC 布線 3D IC

應(yīng)用材料公司推出全新Ioniq? PVD系統(tǒng)助力解決二維微縮下布線電阻難題

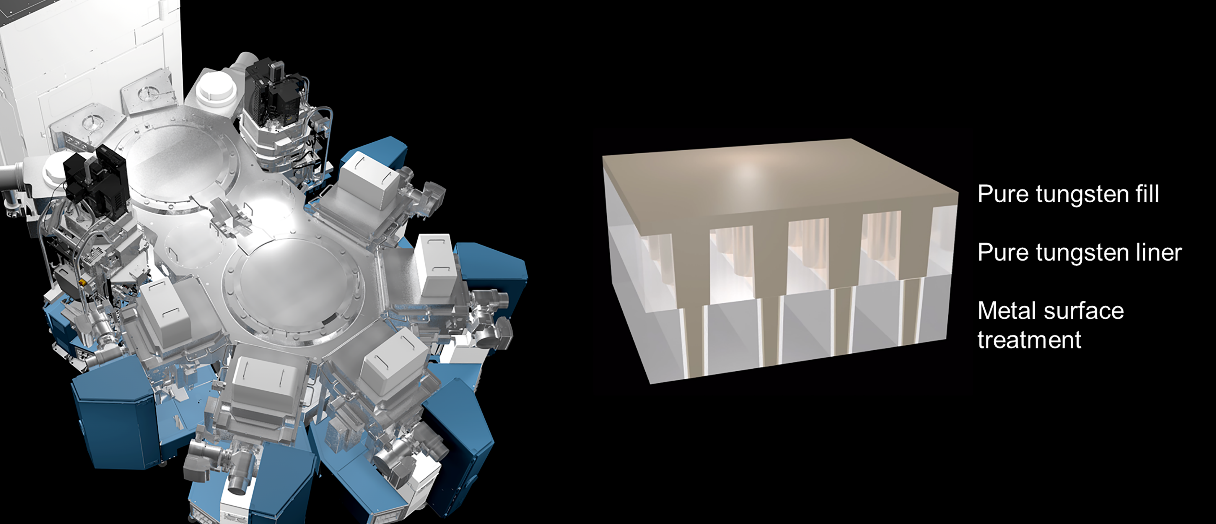

- 應(yīng)用材料公司宣布推出一種全新系統(tǒng),可改進(jìn)晶體管布線沉積工藝,從而大幅降低電阻,突破了芯片在性能提升和功率降低兩方面所面臨的重大瓶頸。芯片制造商正在利用光刻領(lǐng)域的先進(jìn)技術(shù)將芯片制程縮小至3納米及以下節(jié)點(diǎn)。但隨著互連線變細(xì),電阻呈現(xiàn)指數(shù)級(jí)上升,這不僅降低了芯片性能,還增大了功耗。如果該問題無法得到解決,更為先進(jìn)的晶體管帶來的益處將被指數(shù)級(jí)上升的布線電阻完全抵消。芯片布線一般指沉積金屬在介電材料上被刻蝕出的溝槽和通孔內(nèi)的過程。在傳統(tǒng)工藝中,布線沉積使用的金屬疊層通常由以下幾部分構(gòu)成:阻擋層用于防止金屬與介電材料

- 關(guān)鍵字: PVD 布線

開關(guān)電源布線技巧匯總

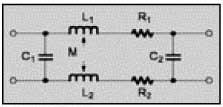

- 開關(guān)電源,又稱交換式電源、開關(guān)變換器,是一種高頻化電能轉(zhuǎn)換裝置,是電源供應(yīng)器的一種。熔開關(guān)電源利用的切換晶體管多半是在全開模式及全閉模式之間切換,這兩個(gè)模式都有低耗散的特點(diǎn),切換之間的轉(zhuǎn)換會(huì)有較高的耗散,但時(shí)間很短,所以民熔開關(guān)電源比較節(jié)省能源,產(chǎn)生廢熱較少。民熔開關(guān)電源的高轉(zhuǎn)換效率是其一大優(yōu)點(diǎn),而民熔開關(guān)電源工作頻率高,也可以使用小尺寸、輕重量的變壓器,熔開關(guān)電源重量也會(huì)比較輕。民熔開關(guān)電源產(chǎn)品廣泛應(yīng)用于工業(yè)自動(dòng)化控制、軍工設(shè)備、科研設(shè)備、LED照明等領(lǐng)域。 而在開關(guān)電源,布線一直是一個(gè)老生常談的

- 關(guān)鍵字: 開關(guān)電源 布線

PCB層疊設(shè)計(jì)入門基本原則

- PCB設(shè)計(jì)工程師在完成預(yù)布局后,重點(diǎn)需要對(duì)板子布線瓶頸處進(jìn)行分析,再結(jié)合PCB設(shè)計(jì)軟件關(guān)于布線要求來確定布線層數(shù),綜合單板的性能指標(biāo)要求與成本承受

- 關(guān)鍵字: PCB設(shè)計(jì) 布線 層疊設(shè)計(jì)

PCB工程師面試題,看看你都會(huì)嗎?

- 以下是深圳某公司的PCB工程師面試題目,來試下你會(huì)幾題。(答案在最下方) 一、填空 1.PCB上的互連線按類型可分為()和() 。 2.引起串?dāng)_的兩個(gè)因素是()和()。 3.EMI的三要素:()。 4.1OZ銅 的厚度是()。 5.信號(hào)在PCB(Er為4)帶狀線中的速度為:()。 6.PCB的表面處理方式有:()。 7.信號(hào)沿50歐姆阻抗線傳播.遇到一阻抗突變點(diǎn).此處阻抗為75歐姆.則在此處的信號(hào)反身系數(shù)為()。 8.按IPC標(biāo)準(zhǔn).PTH孔徑公差為:()NPTH孔

- 關(guān)鍵字: PCB 布線

PCB設(shè)計(jì)中,布局布線有哪些基本原則

- 一、元件布局基本規(guī)則 1. 按電路模塊進(jìn)行布局,實(shí)現(xiàn)同一功能的相關(guān)電路稱為一個(gè)模塊,電路模塊中的元件應(yīng)采用就近集中原則,同時(shí)數(shù)字電路和模擬電路分開; 2.定位孔、標(biāo)準(zhǔn)孔等非安裝孔周圍1.27mm 內(nèi)不得貼裝元、器件,螺釘?shù)劝惭b孔周圍3.5mm(對(duì)于M2.5)、4mm(對(duì)于M3)內(nèi)不得貼裝元器件; 3. 臥裝電阻、電感(插件)、電解電容等元件的下方避免布過孔,以免波峰焊后過孔與元件殼體短路; 4. 元器件的外側(cè)距板邊的距離為5mm; 5. 貼裝

- 關(guān)鍵字: PCB 布線

?布線介紹

您好,目前還沒有人創(chuàng)建詞條?布線!

歡迎您創(chuàng)建該詞條,闡述對(duì)?布線的理解,并與今后在此搜索?布線的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)?布線的理解,并與今后在此搜索?布線的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司