- 引言

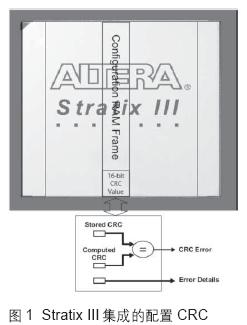

隨著工藝技術的迅速發展,創新進一步提高了器件在速率、容量和功耗等方面的性能,使得FPGA比ASIC更具優勢。然而,技術的發展也突出了以前可以忽略的某些效應,例如,單事件干擾(SEU)導致的軟誤碼影響越來越大。通過仔細的IC設計,65nm節點單位比特的軟誤碼率有所下降,但是每一工藝節點的邏輯容量在不斷翻倍,配置RAM(CRAM)比特數量也隨之增長。

現在的FPGA容量越來越大,功能越來越強,逐漸擔負起系統的核心功能,例如數據通路等;因此,設計人員能夠將系統集成在一片可編程芯片中。這些發

- 關鍵字:

SEU 干擾率

干擾率介紹

您好,目前還沒有人創建詞條干擾率!

歡迎您創建該詞條,闡述對干擾率的理解,并與今后在此搜索干擾率的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473