片上網絡(noc) 文章 最新資訊

AI自動化構建更優(yōu)質的NoCs

- 片上網絡(NoC)是當下系統(tǒng)級芯片(SoC)解決方案的核心組成部分,這類 SoC 通常集成了圖形處理器(GPU)、人工智能加速器,以及由存儲器和中央處理器(CPU)構成的核心模塊。絕大多數電子設計自動化(EDA)工程師極少從零開始自主設計片上網絡。Arteris 公司的 FlexNoC 是一款 EDA 工具,可根據工程師的設計規(guī)范生成片上網絡邏輯,實現(xiàn)芯片內部各組件的互連。工程師只需定義組件間的連接關系與所需功能,后續(xù)的細節(jié)實現(xiàn)均由 FlexNoC 完成。該工具支持硬模塊化和軟模塊化設計,同時融入人工智能

- 關鍵字: 片上網絡 Arteris FlexNoC EDA

通過智能NoC自動化打破SoC設計的壁壘

- 半導體設計的發(fā)展推動了現(xiàn)代片上系統(tǒng)(SoC)達到前所未有的復雜程度。當今最先進的SoC通常集成數百個智能屬性(IP)塊,涵蓋多個處理單元、專用加速器和高速互連。這一快速擴展還得益于多芯片架構的興起,旨在將擴展性和性能擴展到傳統(tǒng)單片設計的限制之外。這些進步帶來了重大挑戰(zhàn),尤其是在管理實現(xiàn)芯片間無縫數據流的互連結構方面。傳統(tǒng)的互連解決方案,如交叉開關和總線架構,已被片上網絡(NoC)取代,后者提供可擴展的高帶寬通信,同時優(yōu)化電力效率。不過,工程師仍需手動實現(xiàn)NoC設計的某些方面,使得工藝勞動強度較大。任何設計

- 關鍵字: SoC 自動化 機器學習 NoC

Arteris將為AMD新一代AI芯粒設計提供FlexGen智能片上網絡 (NoC) IP

- 在AI計算需求重塑半導體市場的背景下。致力于加速系統(tǒng)級芯片 (SoC) 開發(fā)的領先系統(tǒng) IP 提供商 Arteris 公司近日宣布,高性能與自適應計算領域的全球領導者 AMD(納斯達克股票代碼:AMD)已在其新一代AI 芯粒設計中采用FlexGen片上網絡互連IP。Arteris的這項智能NoC IP技術將為 AMD 芯粒提供高性能數據傳輸支持,賦能AMD從數據中心到邊緣及終端設備的廣泛產品組合中的AI應用。Arteris FlexGen NoC IP與AMD Infinity Fabric?互連技術的戰(zhàn)

- 關鍵字: Arteris AMD AI芯粒 片上網絡 NoC IP

芯馳科技擴大Arteris NoC IP技術授權

- 致力于加速系統(tǒng)級芯片(SoC)創(chuàng)建的系統(tǒng)IP領先供應商 Arteris, Inc.近日宣布,芯馳科技(SemiDrive)已擴大對Arteris片上網絡(NoC)IP技術的授權許可。該經過硅驗證的NoC IP技術將被用于解決芯馳科技(SemiDrive)開發(fā)的復雜SoC設計中的互連挑戰(zhàn)。性能要求與國際安全標準正推動車規(guī)級芯片市場持續(xù)擴張。芯馳科技專注于為中央計算及區(qū)域控制式電子電氣架構提供芯片產品和解決方案,其產品線全面覆蓋智能座艙與智能車控兩大核心領域。芯馳科技于2019年首次獲得Arteris片上網絡

- 關鍵字: 芯馳 Arteris NoC

Cadence擴充系統(tǒng)IP產品組合,推出NoC以優(yōu)化電子系統(tǒng)連接性

- 楷登電子(美國Cadence公司)近日宣布擴充其系統(tǒng) IP 產品組合,新增了 Cadence? Janus? Network-on-Chip(NoC)。隨著當今計算需求的不斷提高,更大、更復雜的系統(tǒng)級芯片(SoC)和分解式多芯片系統(tǒng)在市場上迅速普及,硅組件內部和硅組件之間的數據傳輸變得越來越具有挑戰(zhàn)性,功率、性能和面積(PPA)受到了影響。Cadence Janus NoC 能夠以極低的延遲高效管理這些同步高速通信,幫助客戶以更低的風險更快地實現(xiàn)其 PPA 目標。“Cadence是IP和設計質量領域備受信

- 關鍵字: Cadence 系統(tǒng)IP NoC 電子系統(tǒng)連接性

利用搭載全域硬2D NoC的FPGA器件去完美實現(xiàn)智能化所需的高帶寬低延遲計算

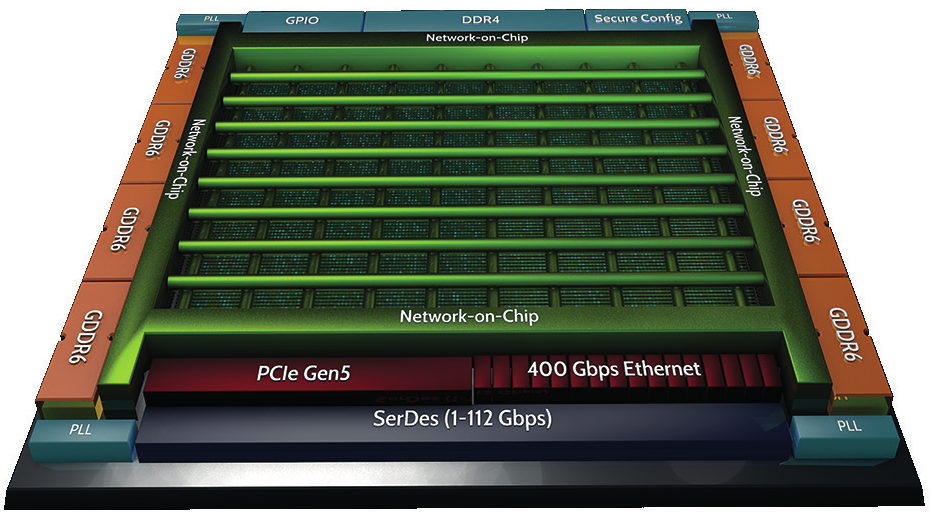

- 隨著大模型、高性能計算、量化交易和自動駕駛等大數據量和低延遲計算場景不斷涌現(xiàn),加速數據處理的需求日益增長,對計算器件和硬件平臺提出的要求也越來越高。發(fā)揮核心器件內部每一個計算單元的作用,以更大帶寬連接內外部存儲和周邊計算以及網絡資源,已經成為智能化技術的一個重要趨勢。這使得片上網絡(Network-on-Chip)這項已被提及多年,但工程上卻不容易實現(xiàn)的技術再次受到關注。作為一種被廣泛使用的硬件處理加速器,F(xiàn)PGA可以加速聯(lián)網、運算和存儲,其優(yōu)點包括計算速度與ASIC相仿,也具備了高度的靈活性,能夠為數據

- 關鍵字: 2D NoC FPGA

Achronix在其先進FPGA中集成2D NoC以支持高帶寬設計(WP028)

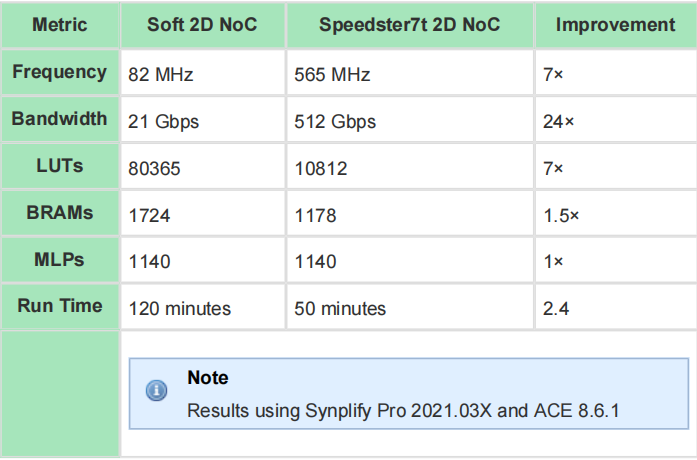

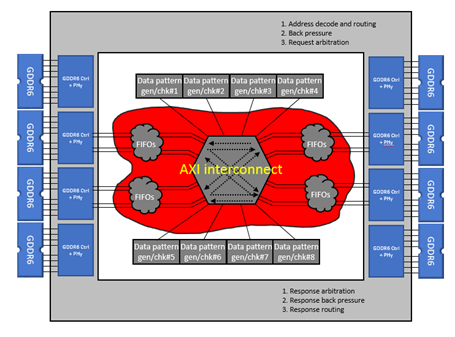

- 摘要隨著旨在解決現(xiàn)代算法加速工作負載的設備越來越多,就必須能夠在高速接口之間和整個器件中有效地移動高帶寬數據流。Achronix的Speedster?7t獨立FPGA芯片可以通過集成全新的、高度創(chuàng)新的二維片上網絡(2D NoC)來處理這些高帶寬數據流。Achronix的FPGA中特有的2D NoC實現(xiàn)是一種創(chuàng)新,它與用可編程邏輯資源來實現(xiàn)2D NoC的傳統(tǒng)方法相比,有哪些創(chuàng)新和價值呢?本白皮書討論了這兩種實現(xiàn)2D NoC的方法,并提供了一個示例設計,以展示與軟2D NoC實現(xiàn)相比,Achronix 2D

- 關鍵字: Achronix FPGA 2D NoC

在FPGA設計中如何充分利用NoC資源去支撐創(chuàng)新應用設計

- 日益增長的數據加速需求對硬件平臺提出了越來越高的要求,F(xiàn)PGA作為一種可編程可定制化的高性能硬件發(fā)揮著越來越重要的作用。近年來,高端FPGA芯片采用了越來越多的Hard IP去提升FPGA外圍的數據傳輸帶寬以及存儲器帶寬。但是在FPGA內部,可編程邏輯部分隨著工藝提升而不斷進步的同時,內外部數據交換性能的提升并沒有那么明顯,所以FPGA內部數據的交換越來越成為數據傳輸的瓶頸。為了解決這一問題,Achronix 在其最新基于臺積電(TSMC)7nm FinFET工藝的Speedster7t FPGA器件中包

- 關鍵字: NoC

片上網絡(NoC)技術的發(fā)展及其給高端FPGA帶來的優(yōu)勢

- 1. 概述在摩爾定律的推動下,集成電路工藝取得了高速發(fā)展,單位面積上的晶體管數量不斷增加。片上系統(tǒng)(System-on-Chip,SoC)具有集成度高、功耗低、成本低等優(yōu)勢,已經成為大規(guī)模集成電路系統(tǒng)設計的主流方向,解決了通信、圖像、計算、消費電子等領域的眾多挑戰(zhàn)性的難題。?隨著片上系統(tǒng)SoC的應用需求越來越豐富,SoC需要集成越來越多的不同應用的IP(Intellectual Property)。另外,片上多核系統(tǒng)MPSoC(MultiProcessor-System-on-Chip)也已經成

- 關鍵字: NoC SoC

片上網絡(noc)介紹

您好,目前還沒有人創(chuàng)建詞條片上網絡(noc)!

歡迎您創(chuàng)建該詞條,闡述對片上網絡(noc)的理解,并與今后在此搜索片上網絡(noc)的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對片上網絡(noc)的理解,并與今后在此搜索片上網絡(noc)的朋友們分享。 創(chuàng)建詞條

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司