利用LVDS緩沖器克服高速信號路徑阻抗不連續之挑戰

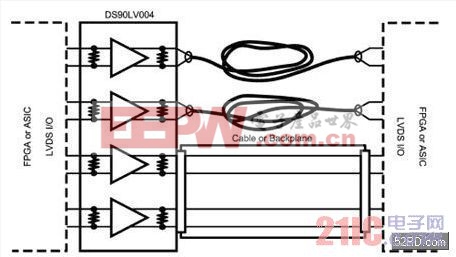

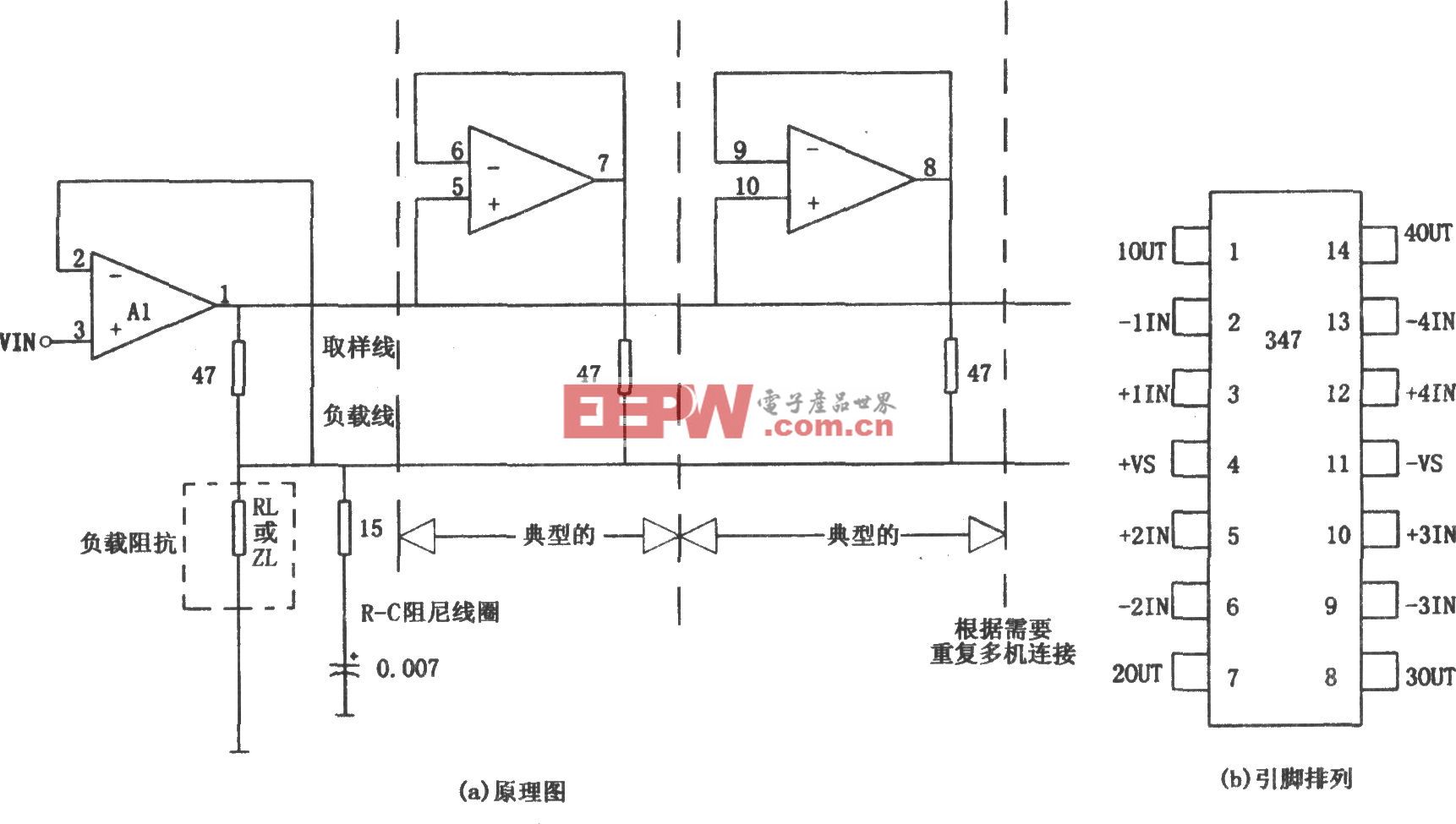

圖6U四通道1.5 Gbps LVDS的緩沖器/中繼器典型應用。

LVDS緩沖器具有帶電插接保護及15kV靜電釋放保護功能,可以加強底板及電纜的抗干擾能力,能保證現場可編程式陣列(FPGA)及專用積體電路(ASIC)傳送的信號的完整性。其應用范圍包括電信、資料通信、工業系統、醫療設備、汽車電子系統及辦公室圖像系統等,典型應用如圖6所示。LVDS緩沖器可以透過普通的底板或簡單的電纜配置驅動4個LVDS時鐘及/或資料通道。由于這款晶片的位差輸入電壓范圍較寬,因此很易接受LVDS、低電壓正射極耦合邏輯(LVPECL)或電流模式邏輯的輸入電平,而且輸出電平完全符合LVDS的規格要求。

做為范例的LVDS緩沖器晶片的資料傳輸率高達1.5Gbps,而且系統設計工程師更可利用這款晶片的可配置輸出預增強功能將輸出加以“加強驅動力”,以便為容易出現信號損耗的互連線路提供補償。此外,對于必須盡量節省用電的應用(如冗余應用),若晶片的4條通道都暫停操作,系統可以透過低功耗模式將功耗降至最低。

總結

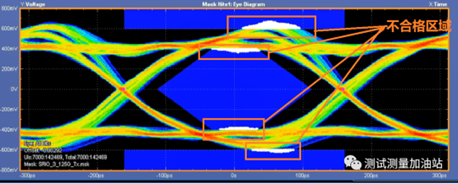

跨底板的高速介面需要在整個信號路徑上控制阻抗。采用簡單型LVDS緩沖器來隔離阻抗不連續或者縮短互聯長度可以降低系統成本;并且也因為不需使用高成本的高頻連接器,進一步提升介面的運作效能。

評論