arm+fpga 文章 最新資訊

FPGA四大設(shè)計(jì)要點(diǎn)解析及應(yīng)用方案集錦

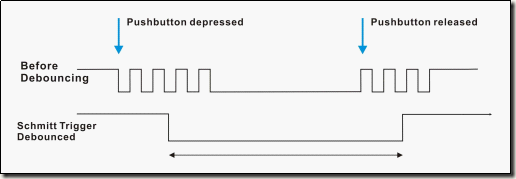

- 本文敘述概括了FPGA應(yīng)用設(shè)計(jì)中的要點(diǎn),包括,時(shí)鐘樹、FSM、latch、邏輯仿真四個部分。 FPGA的用處比我們平時(shí)想象的用處更廣泛,原因在于其中集成的模塊種類更多,而不僅僅是原來的簡單邏輯單元(LE)。早期的FPGA相對比較簡單,所有的功能單元僅僅由管腳、內(nèi)部buffer、LE、RAM構(gòu)建而成,LE由LUT(查找表)和D觸發(fā)器構(gòu)成,RAM也往往容量非常小。現(xiàn)在的FPGA不僅包含以前的LE,RAM也更大更快更靈活,管教IOB也更加的復(fù)雜,支持的IO類型也更多,而且內(nèi)部還集成了一些特殊功能單元,

- 關(guān)鍵字: FPGA FSM 時(shí)鐘樹 仿真

權(quán)威調(diào)查(七):軟件是促成更多客戶使用FPGA的原因

- Xilinx亞太區(qū)銷售及市場副總裁楊飛在2014歲末如此總結(jié):以前FPGA廠商的目標(biāo)是填補(bǔ)ASIC和ASSP空白,現(xiàn)在我們說取代ASIC、ASSP,而我們現(xiàn)在要做的就是,不僅是硬件,還有軟件方面,讓系統(tǒng)級的架構(gòu)工程師和軟件編程工程師也能夠直接使用FPGA。 Xilinx亞太區(qū)銷售及市場副總裁楊飛 因?yàn)镕PGA到今天為止,從來不乏風(fēng)險(xiǎn)投資公司的介入,但是三十多年以來,初創(chuàng)企業(yè)總是做不成、長不大,根本原因和最大挑戰(zhàn)不是說FPGA公司是硬件公司,因?yàn)槲覀兏臼且患腋丬浖墓尽PGA就是把硬件變成軟件

- 關(guān)鍵字: Xilinx FPGA NI

ARM推出安全文件集加速Cortex-R5處理器進(jìn)軍汽車、醫(yī)療與工業(yè)應(yīng)用市場

- ARM®近日針對Cortex®-R5處理器推出一套完整的安全文件集,加速安全關(guān)鍵的相關(guān)應(yīng)用采用Cortex-R5處理器。這對于包括汽車、醫(yī)療與工業(yè)應(yīng)用等產(chǎn)業(yè)而言,是相當(dāng)重要的轉(zhuǎn)變,意味著這些產(chǎn)業(yè)將能以更具成本效益的方式配置先進(jìn)系統(tǒng)。 Cortex-R5 是ARM處理器系列中第一個提供安全文件集的處理器,芯片伙伴可以通過這套文件集證明其產(chǎn)品與新的功能安全標(biāo)準(zhǔn)完全兼容。 ARM處理器事業(yè)部總經(jīng)理Noel Hurley表示,“功能安全對于汽車、醫(yī)療與工業(yè)應(yīng)用等市場日益重要,

- 關(guān)鍵字: ARM Cortex-R5

在使用CNN算法的云數(shù)據(jù)中心,Altera FPGA實(shí)現(xiàn)的加速功能具有優(yōu)異的每瓦性能

- Altera公司今天宣布,微軟采用Altera Arria® 10 FPGA (現(xiàn)場可編程門陣列)實(shí)現(xiàn)基于CNN (卷積神經(jīng)網(wǎng)絡(luò))算法的數(shù)據(jù)中心加速功能,其每瓦性能非常優(yōu)異。這些算法通常用于圖像分類、圖像識別,以及自然語言處理等。 微軟研究人員在云技術(shù)上不斷取得進(jìn)展,采用Arria 10開發(fā)套件和Arria 10 FPGA工程樣片,展示了每瓦40 GFLOPS的性能——數(shù)據(jù)中心業(yè)界最好的性能水平。而且,與GPGPU相比,在CNN平臺上,這一FPGA的性能功耗比是C

- 關(guān)鍵字: Altera FPGA

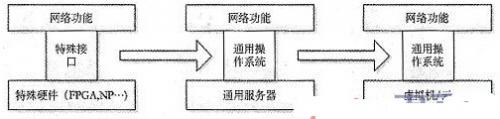

一種面向云架構(gòu)的高性能網(wǎng)絡(luò)接口實(shí)現(xiàn)技術(shù)

- 0概述 在傳統(tǒng)的電信IT產(chǎn)品中,高性能網(wǎng)絡(luò)接口一般采用特殊的硬件模塊來實(shí)現(xiàn),比如網(wǎng)絡(luò)處理器、ASIC、FPGA等等。這些特殊硬件模塊一般會采用特殊的架構(gòu)和指令集對網(wǎng)絡(luò)數(shù)據(jù)收發(fā)過程進(jìn)行優(yōu)化以達(dá)到更好的性能。然而,這也相應(yīng)使得開發(fā)和維護(hù)這些模塊的成本非常的昂貴,同時(shí)還有一個無法解決的問題是基于這些特殊硬件模塊實(shí)現(xiàn)的網(wǎng)絡(luò)接口不能移植到云中,因?yàn)樗鼈兏布鸟詈隙忍吡恕D柖傻某霈F(xiàn),使得通用處理器的性能得到了極大的提升,這也為基于通用處理器實(shí)現(xiàn)高性能網(wǎng)絡(luò)接口提供了可能,同時(shí)也為移植到云中提供了前提條

- 關(guān)鍵字: 網(wǎng)絡(luò)接口 FPGA

蘋果再次擴(kuò)招芯片工程師 或?qū)⑼艫RM版Mac

- 據(jù)《華爾街日報(bào)》的報(bào)道,蘋果近段時(shí)間積極在以色列挖掘芯片設(shè)計(jì)工程師,以便壯大其芯片設(shè)計(jì)部門。報(bào)道稱,目前已經(jīng)有一大批原本在德州儀器任職的以色列工程師跳槽至蘋果。《華爾街日報(bào)》指出,蘋果擴(kuò)招芯片工程師的目的是想要減少對供應(yīng)鏈的依賴,讓自家產(chǎn)品顯得更獨(dú)立。 蘋果再次擴(kuò)招芯片工程師 或?qū)⑼艫RM版Mac 據(jù)了解,蘋果新聘的工程師專長涉及處理芯片、Wi-Fi芯片、閃存芯片等等。 說來很巧,就在《華爾街日報(bào)》的報(bào)道出爐之時(shí),蘋果CEO蒂姆·庫克正在進(jìn)行

- 關(guān)鍵字: 蘋果 ARM

Altera宣布通過與Mentor Graphics合作,推出業(yè)界領(lǐng)先的SoC FPGA系列產(chǎn)品虛擬原型

- Altera公司今天宣布,與Mentor Graphics合作為嵌入式軟件開發(fā)人員提供同類最佳的Vista®虛擬平臺,它支持Altera全系列SoC FPGA,包括具有64位四核ARM® Cortex-A53處理器的第三代14 nm Stratix® 10 SoC。這些先進(jìn)的SoC虛擬平臺加速了整個產(chǎn)品生命周期中嵌入式軟件的開發(fā),顯著縮短了產(chǎn)品面市時(shí)間,同時(shí)降低了成本。 Mentor Graphics Vista SoC虛擬平臺是經(jīng)過預(yù)先開發(fā)的全功能ARM處理器子系統(tǒng)仿真

- 關(guān)鍵字: Altera Mentor Graphics FPGA

Altera發(fā)售20 nm SoC

- Altera公司今天開始發(fā)售其第二代SoC系列,進(jìn)一步鞏固了在SoC FPGA產(chǎn)品上的領(lǐng)先地位。Arria? 10 SoC是業(yè)界唯一在20 nm FPGA架構(gòu)上結(jié)合了ARM?處理器的可編程器件。與前一代SoC FPGA相比,Arria 10 SoC進(jìn)行了全面的改進(jìn),支持實(shí)現(xiàn)性能更好、功耗更低、功能更豐富的嵌入式系統(tǒng)。Altera將在德國紐倫堡舉行的嵌入式世界2015大會上展示其基于SoC的解決方案,包括業(yè)界唯一的20 nm SoC FPGA。 Altera的SoC產(chǎn)品市場資深總監(jiān)

- 關(guān)鍵字: Altera SoC FPGA

工程師分享:如何正確選擇電源模塊?

- 也許你常常會發(fā)現(xiàn)自己面臨相當(dāng)緊張的項(xiàng)目最后期限要求。舉例來說,你的經(jīng)理剛給你布置了為一個新電信系統(tǒng)設(shè)計(jì)電源的任務(wù)。設(shè)計(jì)從在FPGA上實(shí)現(xiàn)的概念證明開始,現(xiàn)在到了必須創(chuàng)造電源的時(shí)候。一個隔離式電源模塊提供12V電源,為先進(jìn)的ASIC、微控制器、FPGA和各種其他元件供電。一如既往,這些元件實(shí)際上充滿了電路板的空間,提供充分的電力、穩(wěn)定性、熱性能、低噪聲及可靠性需要挑戰(zhàn)物理定律。而你只有一個星期時(shí)間來創(chuàng)造這個電源。(嘆息)沒錯,就是這樣,好戲開場了! 由于ASIC、微控制器和FPGA的大電流要求,你

- 關(guān)鍵字: FPGA 電源

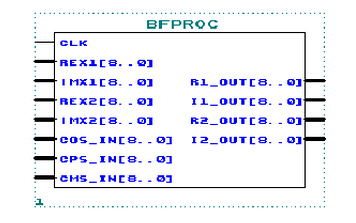

FPGA在數(shù)字信號處理中的簡單應(yīng)用

- 數(shù)字信號處理技術(shù)已經(jīng)成功運(yùn)用于信號地濾波、語音、圖像、音頻、信息系統(tǒng)、控制和儀表設(shè)備。可編程數(shù)字信號處理器在20 世紀(jì)70 年代地引入更是使DSP 技術(shù)突飛猛進(jìn),取得巨大成功,這些PDSP 都是基于精簡指令集(RISC)計(jì)算機(jī)范例的架構(gòu)。它的優(yōu)勢源于大多說信號處理算法的乘-累加運(yùn)算(MAC)都是非常密集的。通過多級流水線架構(gòu),PDSP 可以獲得僅受陣列乘法器的速度限制的MAC 速度。由此可以認(rèn)為FPGA 也能夠用來實(shí)現(xiàn)MAC 單元,且具有速度優(yōu)勢,但是,如果PDSP 能夠滿足所需要的MAC 速度,那么

- 關(guān)鍵字: FPGA 信號處理

FPGA四大設(shè)計(jì)要點(diǎn)解析

- 本文敘述概括了FPGA應(yīng)用設(shè)計(jì)中的要點(diǎn),包括,時(shí)鐘樹、FSM、latch、邏輯仿真四個部分。 FPGA的用處比我們平時(shí)想象的用處更廣泛,原因在于其中集成的模塊種類更多,而不僅僅是原來的簡單邏輯單元(LE)。 早期的FPGA相對比較簡單,所有的功能單元僅僅由管腳、內(nèi)部buffer、LE、RAM構(gòu)建而成,LE由LUT(查找表)和D觸發(fā)器構(gòu)成,RAM也往往容量非常小。 現(xiàn)在的FPGA不僅包含以前的LE,RAM也更大更快更靈活,管教IOB也更加的復(fù)雜,支持的IO類型也更多,而且內(nèi)部還集成了一

- 關(guān)鍵字: FPGA Testbench

經(jīng)驗(yàn)總結(jié):FPGA時(shí)序約束的6種方法

- 對自己的設(shè)計(jì)的實(shí)現(xiàn)方式越了解,對自己的設(shè)計(jì)的時(shí)序要求越了解,對目標(biāo)器件的資源分布和結(jié)構(gòu)越了解,對EDA工具執(zhí)行約束的效果越了解,那么對設(shè)計(jì)的時(shí)序約束目標(biāo)就會越清晰,相應(yīng)地,設(shè)計(jì)的時(shí)序收斂過程就會更可控。 下文總結(jié)了幾種進(jìn)行時(shí)序約束的方法。按照從易到難的順序排列如下: 0. 核心頻率約束 這是最基本的,所以標(biāo)號為0。 1. 核心頻率約束+時(shí)序例外約束 時(shí)序例外約束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時(shí)序

- 關(guān)鍵字: FPGA 時(shí)序約束

arm+fpga介紹

您好,目前還沒有人創(chuàng)建詞條arm+fpga!

歡迎您創(chuàng)建該詞條,闡述對arm+fpga的理解,并與今后在此搜索arm+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對arm+fpga的理解,并與今后在此搜索arm+fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司