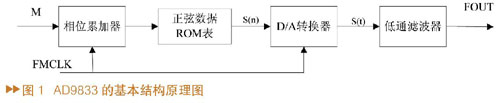

- 為了滿足目前對數據處理速度的需求,設計了一種基于FPGA+DDS的控制系統。闡述了系統硬件實現方法,給出了相關的軟件設計例程。并對DDS AD9911各個控制寄存器的設置與時序進行詳細說明,最后給出了實驗結果。

- 關鍵字:

FPGA DDS 控制設計

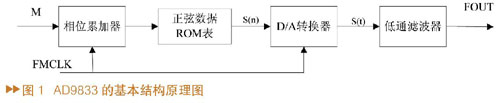

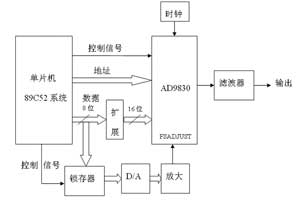

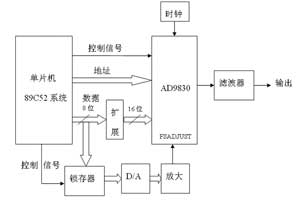

- 提出了一種基于DDS(Direct Digital Synthesize)AD9850的頻率、相位、幅值均可調節的正弦信號發生器。該正弦信號發生器采用AT89S52單片機為控制器,D/A轉換器TLC5615與乘法器AD534相結合。實現輸出正弦信號幅值可控,采用AD8ll控制輸出正弦信號電壓幅值,產生50 H2~3 kHz頻段的正弦波,步進頻率為50 Hz。該信號發生器可應用在交變磁場測量儀和試驗儀器、工程設計的函數發生器中。

- 關鍵字:

DDS 可調 信號發生器 設計 基于 模擬 AD9850 TLC5615

- 多年以來,作為業界主流產品的模擬PLL已被熟知,模擬PLL性能穩定,可為頻率合成和抖動消除提供低成本的解決方案,工作頻率高達8GHz及以上。然而新興的基于直接數字頻率合成(DDS)的數字PLL在某些應用中極具競爭力。本文比較了模擬PLL和基于DDS的數字PLL之間的差異,以及如何利用這些差異來指導設計人員選擇最佳的解決方案。

數字PLL利用數字邏輯實現傳統的PLL模塊。雖然實現數字PLL的方法有很多,但本文只介紹基于DDS的數字PLL架構。

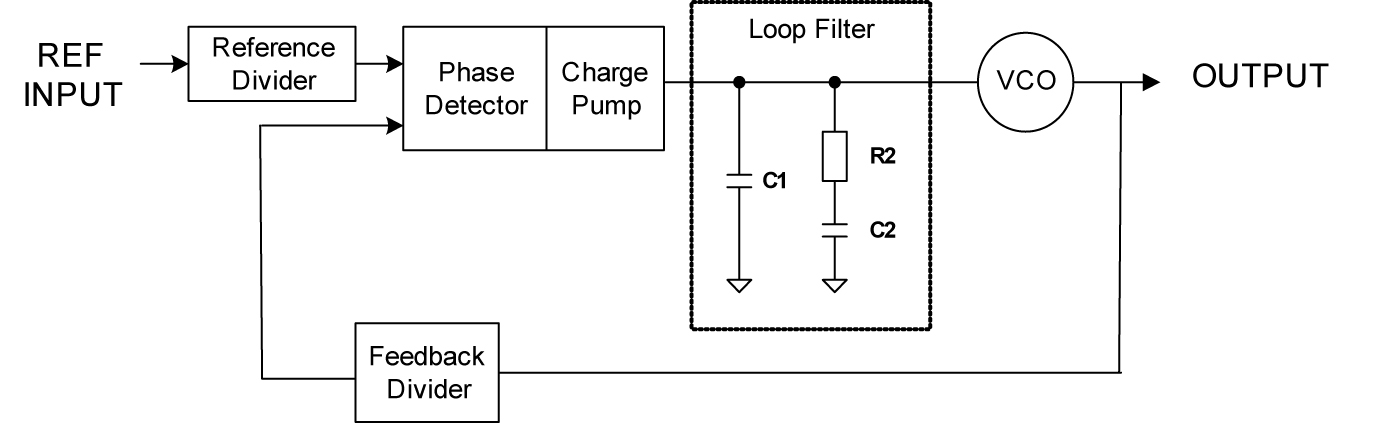

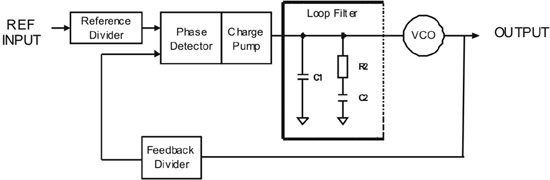

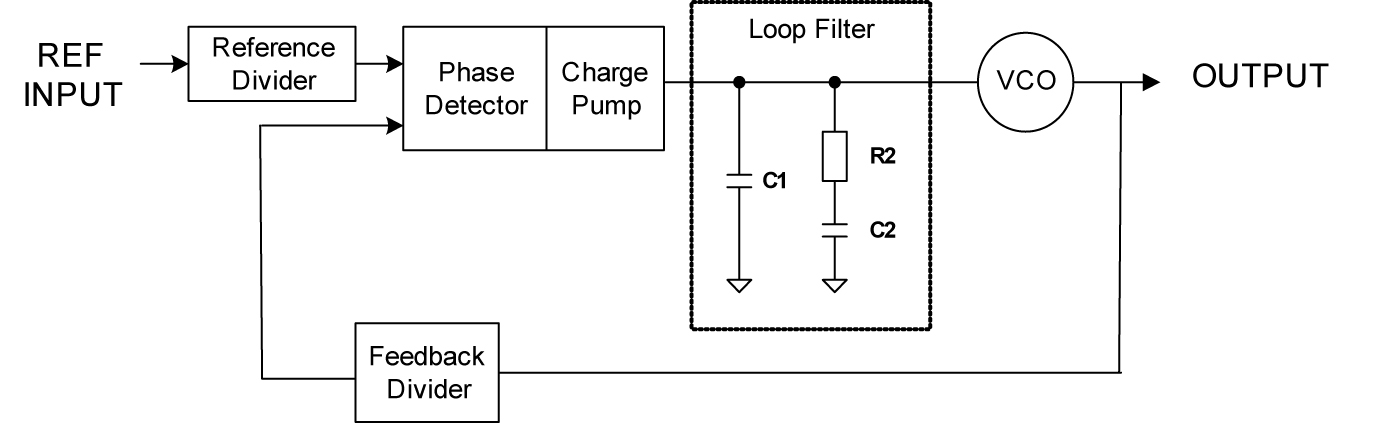

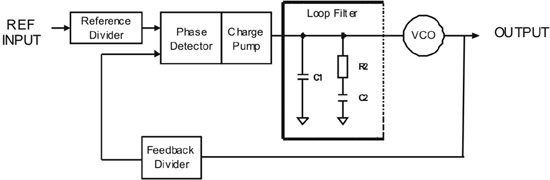

圖1 典型的模擬PLL結構框圖

- 關鍵字:

PLL DDS 分頻器 鑒相器 DAC VCO

- 多年以來,作為業界主流產品的模擬PLL已被熟知,模擬PLL性能穩定,可為頻率合成和抖動消除提供低成本的解決方案,工作頻率高達8GHz及以上。然而新興的基于直接數字頻率合成(DDS)的數字PLL在某些應用中極具競爭力。

數字PLL利用數字邏輯實現傳統的PLL模塊。雖然實現數字PLL的方法有很多,但本文只介紹基于DDS的數字PLL架構。

圖1 典型的模擬PLL結構框圖

圖1所示的是典型的模擬PLL。輸入信號首先進入參考分頻器,參考分頻器可降低輸入鑒相器的信號頻率。在PLL中,參考分頻器的

- 關鍵字:

DDS 數字PLL

- 中國 北京——Analog Devices, Inc.(紐約證券交易所代碼:ADI),全球領先的高性能信號處理解決方案供應商,最新推出一對時鐘發生與分配IC——AD9520與AD9522,實現了業界最佳的器件集成度、低噪聲、低抖動性能與信號輸出靈活性的完美組合。 AD9520與AD9522多輸出時鐘發生器內置一個512 Byte的嵌入式EEPROM存儲器模塊,為系統工程師提供了可用作時鐘源和系統時鐘的雙重可編程時鐘解決方案。通過利用片上存儲器對具體的輸出

- 關鍵字:

EEPROM 冗余基準 PLL Analog Devices

- 引言

在數字信息傳輸中,基帶數字信號通常要經過調制器調制,將頻率搬移到適合信息傳輸的頻段上。2FSK就是用數字信號去調制載波的頻率(移頻鍵控),由于它具有方法簡單、易于實現、抗噪聲和抗衰落性能較強等優點,因此在現代數字通信系統的低、中速數據傳輸中得到了廣泛應用。

直接數字頻率合成技術(DDS)將先進的數字處理技術與方法引入信號合成領域。DDS器件采用高速數字電路和高速D/A轉換技術,具備頻率轉換時間短、頻率分辨率高、頻率穩定度高、輸出信號頻率和相位可快速程控切換等優點,可以

- 關鍵字:

數字信號 調制器 DDS 單片機控

- 摘要:基于對我國鐵路主要制式信號的典型參數特征的分析和研究,通過MATLAB仿真軟件建立我國主要制式信號的數學模型,在重點解決邊頻精度、相位連續、差分放大等關鍵問題的前提下,提出采用DDS直接數字頻率合成技術生成我國鐵路專用2FSK(二進制頻移鍵控)調制信號的新方法,并給出相關的硬件、軟件設計。

關鍵詞:鐵路信號;直接數字頻率合成;頻移鍵控

2008年5月12日收到本文。郜洪民:助理研究員,從事鐵路列車自動控制研究。

引言

隨著我國鐵路客運專線、高速鐵路建設步伐的加快,研究開發以一體化、網

- 關鍵字:

DDS 鐵路信號 直接數字頻率合成 頻移鍵控 200809

- DDS技術作為一種先進的直接數字頻率合成技術,用數字控制的方法從一個頻率基準源產生多種頻率,具有高可靠性、高集成度、高頻率分辨率及頻率變化快、控制靈活等特點,在通信與儀表領域得到了廣泛的應用。采用DDS芯片制作的信號源,輸出信號的頻率和幅度都可由微機來精確控制,調節非常方便,常用的幅度調節方法是在DDS輸出端加數字增益控制電路,或者通過改變DAC的參考電壓或編程電阻來實現。本文介紹一種新的幅度控制方法,通過控制DDS的DAC滿刻度電流的大小來實現對輸出幅度的調節,能夠保證DDS的無雜散動態輸出范圍(S

- 關鍵字:

單片機 DDS 數字頻率 SFDR D/A 轉換器

- Maxim推出基于晶體的鎖相環(PLL) VHF/UHF發送器MAX7057,能夠在較寬的頻率范圍內發送OOK/ASK/FSK數據。器件配合適當的晶體頻率,可以發送300MHz至450MHz范圍內的任何信號,并能夠以高達100kbps的速率發送NRZ碼(50kbps曼徹斯特碼)。

MAX7057集成了可編程分數N PLL合成器和寬帶VCO,因而具有極大的靈活性。此外,還可以設置內部電容,實現功率放大器(PA)與天線之間的阻抗匹配。這種拓撲結構可確保多個工作頻率下的高效率傳輸,從而使MAX7057

- 關鍵字:

Maxim PLL 鎖相環 發送器

- CDCE937 和 CDCEL937 均為基于 PLL 模塊的、低成本、高性能的可編程時鐘合成器,可以在單輸入頻率的不同頻率下生成多達七個輸出時鐘。每一個輸出均可以進行系統內編程,從而使用三個獨立的可配置 PLL 就可用于任何高達 230MHz 的時鐘頻率。該器件具有簡單的頻率同步,使零-PPM 時鐘生成成為可能。另外,這兩種合成器還具有擴頻時鐘及片上 EEPROM 和通過 SDA/SCL 進行系統內熱編程的特點。對于數字媒體系統、流媒體、GPS 接收機、便攜式媒體以及DSP/OMAP/DaVinci

- 關鍵字:

TI 時鐘合成器 可編程 PLL

- DDS是一種用來從固定頻率時鐘源產生模擬輸出波形或者時鐘信號的數字技術,AD9959適合要求高達200 MHz的復雜高速頻率合成的應用,包括超寬帶步進頻率雷達、相位陣列雷達和光通信系統。AD9959集成了D/A轉換、SPI和CP,具有頻率轉換時問短、輸出頻帶寬的優點,能夠滿足對低相位噪聲、低雜散噪聲、快速頻率切換以及寬帶線性掃描的要求,還可以應用到跳頻通信中。采用該芯片設計的信號源結構簡單、功能強大、抗干擾性優越,具有良好的性價比。

- 關鍵字:

9959 DDS AD 性能

- 0 引 言

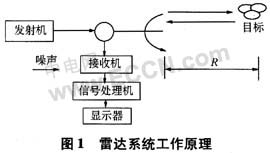

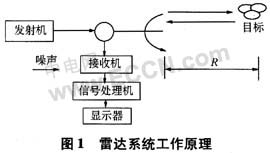

探地雷達是近10年迅速發展起來的一種無損探測新技術,它具有探測速度快、高空間分辨率、對目標的三維電磁特征敏感、可實現連續透視掃描以及二維彩色圖像實時顯示等優點,目前已在工程勘察、水利隱患探測、工程質量檢測、地下管網探測以及考古等領域得到了廣泛應用。

隨著雷達技術的迅速發展,人們對雷達信號的要求也越來越高。高精度、高掃描率、高抗干擾性、低截獲率成為人們追求的目標。滿足這種需求除了靠產生復雜的雷達波形外,還需要在雷達系統中應用高性能的器件。

直接數字頻率合成方法具有傳統方法所

- 關鍵字:

雷達 無損探測 DDS GPR

dds+pll介紹

您好,目前還沒有人創建詞條dds+pll!

歡迎您創建該詞條,闡述對dds+pll的理解,并與今后在此搜索dds+pll的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473