- 該系統由FPGA、單片機控制模塊、鍵盤、LED顯示組成,采用直接數字頻率合成(DDS),D/A以及實時計算波形值等技術,設計出具有頻率設置功能,頻率步進為100 Hz,頻率范圍為1 kHz~10 MHz之間正弦信號發生器。該系統的頻率范圍寬,步進小,頻率精度較高。

- 關鍵字:

FPGA DDS 正弦信號發生器

- 隨國家節能環保推行政策的出臺以及太陽能開發技術的不斷完善,太陽能作為一種綠色的能源逐漸為工業和家庭所用;但如今外設工作復雜多變,對電源(特別是交流電源)的要求越來越嚴峻,本設計針對這一瓶頸提供了一套控制系統,可以有效解決多種環境下的用電。基于MXT8051的太陽能可調逆變電源采用MXT8051做微控制器控制,12864液晶顯示,鍵盤輸入,正弦波頻率、相位及幅值的調制;再由放過充模塊控制太陽能板的充電儲能輸出;正弦波輸出調節模塊由DDS芯片AD98508集成模塊產生可調節波形,再由高頻放大模塊放大輸出。整個

- 關鍵字:

時代民芯 MXT8051 DDS AD9850

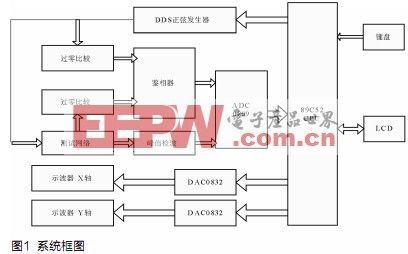

- 本文介紹了基于DDS技術的頻率特性測試儀的設計方法。在設計中掃頻信號源采用DDS芯片AD9851實現,以單片機AT89C52為控制核心,控制整個系統協調工作并實時對所測數據進行處理, LCD顯示幅頻特性和相頻特性曲線,實現了系統的小型化和全數字化。

- 關鍵字:

單片機 測試儀 DDS 幅頻特性 相頻特性 201006

- 在此說明以晶體振蕩器做為基準振蕩器,將其與VCO以及PLL電路組合成為信號產生器的情形也被稱為頻率合成器。

此一PLL-VCO電路的設計規格如表l所示。振蕩頻率范圍為40M~60MHz內的10MHz寬。每一頻率階段(step)寬幅為10

- 關鍵字:

PLL-VCO

- 在通信機等所使用的振蕩電路,其所要求的頻率范圍要廣,且頻率的穩定度要高。

無論多好的LC振蕩電路,其頻率的穩定度,都無法與晶體振蕩電路比較。但是,晶體振蕩器除了可以使用數字電路分頻以外,其頻率幾乎無法

- 關鍵字:

PLL 電路設計 原理

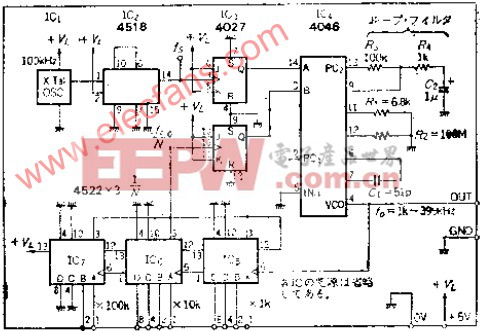

- 電路的功能如果要求振蕩頻率準確、穩定度好,采用石英晶體振蕩器作本振的PLL合成振蕩電路是比較合適的。但本電路采用了C-MOS型的PLL IC(4046),VCO輸出為方波,能以1KHZ為一級在1KHZ~399KHZ范圍內連續變化。全部采

- 關鍵字:

PLL 合成 振蕩 電路 399KHZ 穩定 晶體 振蕩器 等效 頻率

- 電路的功能很多電路都要求把頻率準確地倍增,使用PLL電路可很容易組成滿足這種要求的電路。例如主振頻率為1KHZ,若使用倍增器內插10個脈沖,可變成10KHZ的脈沖信號。在VCO中,即使主振頻率發生變化,也能獲得跟蹤主振

- 關鍵字:

PLL 10 IC的 鎖相環

- ADI全球領先的高性能信號處理解決方案供應商,和提供覆蓋整個 RF 信號鏈的 RF IC 功能模塊的全球領導者,最近宣布發布 ADIsimPLL(TM) 3.3版 ( http://www.analog.com/adisimpll ),這是其大獲成功的鎖相環 (PLL) 電路設計和評估工具的最新版本。ADIsimPLL 3.3版 ( http://www.analog.com/adisimpll ) 可協助用戶對采用 ADI PLL 頻率合成器 ( http://www.analog.com/zh/p

- 關鍵字:

ADI PLL 頻率合成器

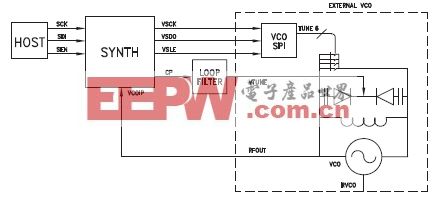

- 頻率源可以說是一個通信系統的心臟,心臟的好壞很大程度上決定著一個機體的健康狀況,而鎖相環又是頻率源的主要組成部分,因此性能優異的鎖相環芯片對于通信系統來說是非常重要的。

鎖相環的相位噪聲對電子設備和電子系統的性能影響很大。從頻域看它分布在載波信號兩旁按冪律譜分布,無論做發射激勵信號,還是接收機本振信號以及各種頻率基準時,這些相位噪聲將在解調過程中都會和信號一樣出現在解調終端,引起基帶信噪比下降,誤碼率增加。

低相噪Hittite鎖相環產品分為集成VCO和沒有集成VCO兩種。集成VCO的PL

- 關鍵字:

世強電訊 PLL 基站類鎖相環

- 首先闡述了DDS技術的基本原理,在此基礎上,實現了一種采用單片機AT89S52控制AD9850芯片的任意信號發生器系統。理論研究和實驗結果表明,該系統可產生頻率和幅值均可調的正弦波、三角波和方波,且頻帶寬、精度高、穩定性好。

- 關鍵字:

DDS 信號發生器

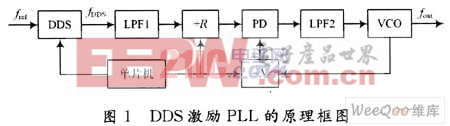

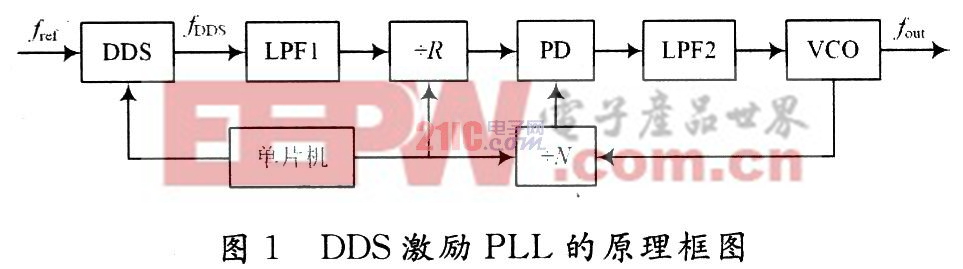

- 基于DDS+PLL高性能頻率合成器的設計與實現,摘要:結合DDS+PLL技術,采用DDS芯片AD9851和集成鎖相芯片ADF4113完成了GSM 1 800 MHz系統中高性能頻率合成器的設計與實現。詳細介紹系統中核心芯片的性能、結構及使用方法,并運用ADS和ADISimPLL軟件對設計方案進行

- 關鍵字:

合成器 設計 實現 頻率 高性能 DDS PLL 基于

- DDS+PLL高性能頻率合成器的設計與實現,摘要:結合DDS+PLL技術,采用DDS芯片AD9851和集成鎖相芯片ADF4113完成了GSM 1 800 MHz系統中高性能頻率合成器的設計與實現。詳細介紹系統中核心芯片的性能、結構及使用方法,并運用ADS和ADISimPLL軟件對設計方案進行

- 關鍵字:

設計 實現 合成器 頻率 PLL 高性能 DDS

- 摘要:利用現場可編程門陣列(FPGA)設計并實現直接數字頻率合成器(DDS)。結合DDS的結構和原理,給出系統設計方法,并推導得到參考頻率與輸出頻率間的關系。DDS具有高穩定度,高分辨率和高轉換速度,同時利用Ahera公司

- 關鍵字:

FPGA DDS

dds+pll介紹

您好,目前還沒有人創建詞條dds+pll!

歡迎您創建該詞條,闡述對dds+pll的理解,并與今后在此搜索dds+pll的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473