- 針對當今電子系統對高速大容量內存的需要,本文闡述了使用DDR控制器IP核來設計實現DDR內存接口的方法。

- 關鍵字:

DDR 內存 接口的設計

- 2007年6月8日,全球領先的運動控制解決方案提供商——丹納赫傳動(Danaher Motion)公司宣布,其創新的Cartridge DDR™系列直接驅動旋轉伺服電機(CDDR)新添三種小框架的新產品,因此,現共有4.25平方英寸到13.78平方英寸五種框架尺寸的CDDR電機供應,每種尺寸各有四個鐵心長度。CDDR是直接驅動技術中非常特別的一種,其特點在于采用預制零部件、完整的工廠對準型高分辨率反饋裝置和獨特的無軸承設計,確保可以在30分鐘內實現即裝即用,且沒有維護成本。

- 關鍵字:

Cartridge DDR 丹納赫 消費電子 消費電子

- 摘要: 本文采用LatticeXP系列FPGA結合IP解決DDR RAM的讀寫控制。并且在硬件上面進行了實際測試。關鍵詞: 嵌入式系統;DDR RAM;FPGA;IP;LattcieXP

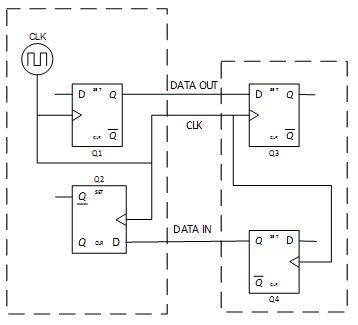

前言隨著高速處理器的不斷發展,嵌入式系統應用的領域越來越廣泛,數字信號處理的規模也越來越大,系統中RAM規模不斷增加,比如視頻監控、圖像數據采集等領域,圖像處理的實時性對RAM帶寬的要求不斷增加,傳統的SDRAM在帶寬上已經逐漸無法滿足應用要求,DDR SDRAM(雙倍速率SDRAM)采用在時鐘CL

- 關鍵字:

0702_A DDR FPGA IP LattcieXP RAM 單片機 嵌入式系統 雜志_設計天地 存儲器

- DDR內存已成為系統DRAM的主要技術,而DDR系統的驗證則是新的數字系統設計最具挑戰性且費時的工作之一。邏輯分析儀是協助工程師驗證這些系統的重要工具,但在成本與空間的限制下,邏輯分析儀探測技術變成了一個值得深思的問題。 理想上,DDR的可測試性應成為最終設計的一部份,以利于在測試臺進行系統的驗證,因為在整個產品生命周期中的工程設計與委外代工都會增加成本。然而礙于邏輯分析儀探測點的電氣負載與空間需求,這種作法直到今天仍不可行。新的免接頭式邏輯分析儀探測技術使DDR可測試性得以結合到產品的最初與最終

- 關鍵字:

DDR 測量 測試

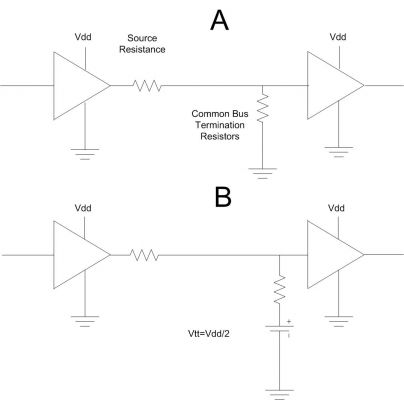

- DDR(雙數據速率)DRAM應用于工作站和服務器的高速存儲系統中。存儲器IC采用1.8V或2.5V電源電壓,并需要等于電源電壓一半的基準電壓(VREF=VDD/2)。此外,各邏輯輸出端都接一只電阻器,等于并跟蹤VREF的終端電壓VTT。在保持VTT=VREF+0.04V的同時,必須提供源流或吸收電流。圖1所示電路可為1.8V和2.5V兩種存儲器系統提供終端電壓,并可輸出高達6A的電流。IC1有一個降壓控制器和2個線性穩壓控制器。IC1在輸入電壓為4.5~28V下工作。

- 關鍵字:

電源電路 DDR DRAM 存儲器

- 電子系統設計師很少考慮他們下一個設計中元器件的成本,而更關注它們能夠達到的最高性能。

- 關鍵字:

DDR 存儲器 接口設計

- 本設計介紹了一種應用于DDR內存系統的獨特、低成本的電源電路。常規DDR內存系統包括一個雙反向轉換器和一個輸出參考電壓。與常規設計不同,本文用線性調節器代替反向轉換器,見圖1,具有消除PWM轉換器開關噪聲的優點。DDR內存系統要求穩定的2.5V主電源(VDD)、端電壓(VTT)和參考電壓(VREF),其中VDD、VTT可引出和吸收電流,,這些要求給電源設計者帶來新挑戰。本電路中,低壓同步反向器產生8A,2.5V的主電源VDD輸出,VTT和VREF通過運放的線性調節設計實現。電路專門為低功耗DDR系統(如p

- 關鍵字:

DDR 存儲器

designware ddr介紹

您好,目前還沒有人創建詞條designware ddr!

歡迎您創建該詞條,闡述對designware ddr的理解,并與今后在此搜索designware ddr的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473