designware ddr 文章 最新資訊

NVIDIA選用新思科技經(jīng)驗證DesignWare DDR IP核

- 重點:高質(zhì)量DesignWare DDR PHY IP核為NVIDIA提供無與倫比的性能、延遲和電源效率DDR PHY支持DDR5/4的每個通道多個DIMM,滿足NVIDIA的網(wǎng)絡數(shù)據(jù)速率和內(nèi)存容量要求基于固件的現(xiàn)場可升級訓練可提高通道的穩(wěn)定性和可靠性,并且有助于算法更新,從而降低采用新內(nèi)存協(xié)議的風險新思科技(Synopsys, Inc.)近日宣布,NVIDIA的網(wǎng)絡業(yè)務部門Mellanox將采用經(jīng)驗證的DesignWare? DDR5/4 PHY IP核,以滿足其針對高性能計算和人工智能應用的Infin

- 關(guān)鍵字: 云計算 NVIDIA 新思科技 DesignWare DDR IP核

新思科技VCS被Graphcore采用

- 新思科技宣布,Graphcore采用新思科技基于Verdi?調(diào)試的VCS?仿真解決方案,驗證其最近推出Colossus? GC200智能處理單元(IPU),該產(chǎn)品足以改變行業(yè)游戲規(guī)則。Graphcore的第二代IPU是有史以來最復雜的微處理器,擁用594億個晶體管和1472個獨立處理器內(nèi)核。新思科技VCS讓Graphcore能夠為其大規(guī)模平行IPU設計,特別針對機器智能(machine intelligence)工作負載,顯著提高仿真吞吐量。Graphcore芯片業(yè)務副總裁Phi

- 關(guān)鍵字: Tenstorrent 新思科技 DesignWare IP AI

Tenstorrent采用新思科技的廣泛DesignWare IP組合

- 重點:Tenstorrent采用DesignWare PCI Express 4.0、ARC HS48處理器和LPDDR4 IP,一次性完成其Graysull 人工智能(AI)處理器芯片的硅晶設計PCI Express 4.0控制器與PHY IP達到最高x16鏈接寬度,可處理超過36dB的信道損耗,提供低延遲和高吞吐量連接采用超標量架構(gòu)的四核ARC HS48處理器IP提供卓越的節(jié)能性能和可擴展性低延遲LPDDR4控制器IP提供內(nèi)存電源狀態(tài)的自動優(yōu)化,以實現(xiàn)低功耗以及高可靠性的高級RAS功能新思科技(Syn

- 關(guān)鍵字: Tenstorrent 新思科技 DesignWare IP AI

燦芯半導體為NVDIMM OEM提供完整解決方案

- 國際領(lǐng)先的定制化芯片(ASIC)設計方案提供商及DDR控制器和物理層IP供應商——燦芯半導體(上海)有限公司(以下簡稱“燦芯半導體”)近日對外宣布為一家著名的NVDIMM供應商提供完整的NVDIMM控制器芯片解決方案。非易失性雙列直插式內(nèi)存模塊(NVDIMM)是計算機的一種隨機存取存儲器,即使在遇到供電不穩(wěn)、系統(tǒng)崩潰或正常關(guān)機等斷電情況時仍保留其內(nèi)容。NVDIMM可快速恢復現(xiàn)場,提高應用程序性能,數(shù)據(jù)安全性和系統(tǒng)崩潰修復時間,加強了固態(tài)驅(qū)動器(SSD)的耐用性和可靠性。當前,大多數(shù)NVDIMM控制器采用F

- 關(guān)鍵字: OEM DDR SSD ASIC

瓴盛科技選用新思科技DesignWare IP核加速新一代SoC開發(fā)

- 摘要瓴盛科技采用新思科技廣泛的DesignWare IP核組合來降低風險并加快新一代移動芯片組上市用于USB、MIPI和DDR的高品質(zhì)DesignWare IP已幫助億萬片上系統(tǒng)實現(xiàn)量產(chǎn)雙方的長期合作助力瓴盛科技的SoC設計一次性流片成功和量產(chǎn)新思科技(Synopsys, Inc.,納斯達克股票代碼:SNPS)今天宣布瓴盛科技(JLQ Technology Co., Ltd.)已經(jīng)選用新思科技DesignWare? Interface IP核來加速其面向一系列應用的新一代高性能、低功耗SoC芯片的開發(fā)。瓴

- 關(guān)鍵字: 瓴盛科技 新思科技 DesignWare IP SoC

DDR硬件設計要點都在這里

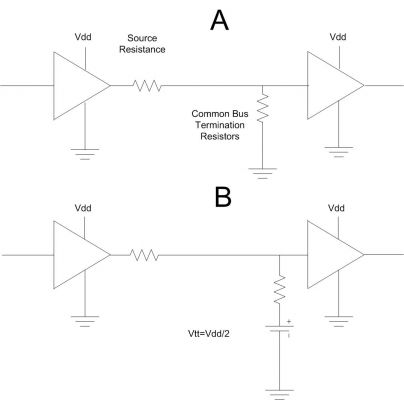

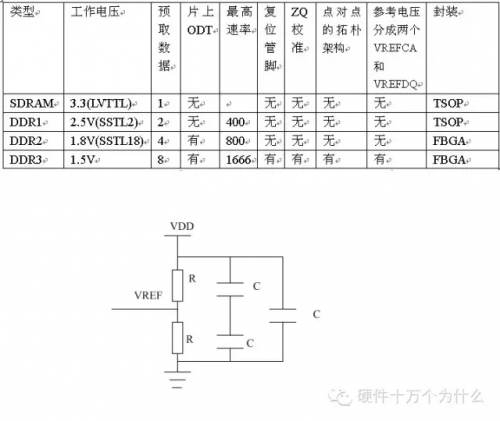

- DDR硬件設計要點 1. 電源 DDR的電源可以分為三類: a主電源VDD和VDDQ,主電源的要求是VDDQ=VDD,VDDQ是給IO buffer供電的電源,VDD是給但是一般的使用中都是把VDDQ和VDD合成一個電源使用。 有的芯片還有VDDL,是給DLL供電的,也和VDD使用同一電源即可。電源設計時,需要考慮電壓,電流是否滿足要求,電源的上電順序和電源的上電時間,單調(diào)性等。電源電壓的要求一般在±5%以內(nèi)。電流需要根據(jù)使用的不同芯片,及芯片個數(shù)等進行計算。由于DDR的電流一般都比較大,所以P

- 關(guān)鍵字: DDR,PCB

控制DDR線長匹配來保證時序,在PCB設計時應該這么做!

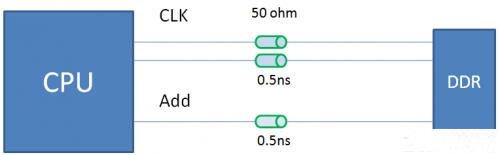

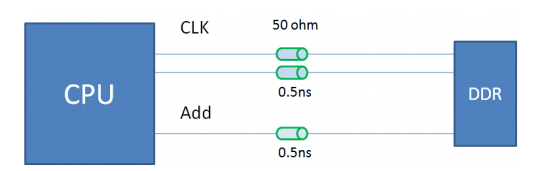

- DDR布線在PCB設計中占有舉足輕重的地位,設計成功的關(guān)鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,線長匹配又是一個重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號與時鐘做等長。數(shù)據(jù)信號與DQS做等長。為啥要做等長?大家會說是要讓同組信號同時到達接收端,好讓接收芯片能夠同時處理這些信號。那么,時鐘信號和地址同時到達接收端,波形的對應關(guān)系是什么樣的呢?我們通過仿真來看一下具體波形。 建立如下通道,分別模擬DDR3的地址信號與時鐘信號。

- 關(guān)鍵字: PCB DDR

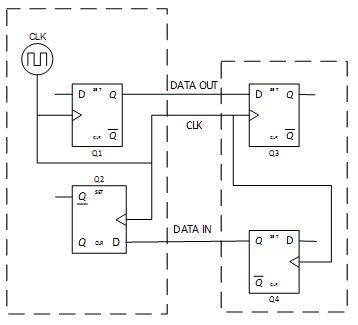

DDR布線舉足輕重,一文看懂背后的大學問

- DDR布線在PCB設計中占有舉足輕重的地位,設計成功的關(guān)鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,線長匹配又是一個重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號與時鐘做等長。數(shù)據(jù)信號與DQS做等長。為啥要做等長?大家會說是要讓同組信號同時到達接收端,好讓接收芯片能夠同時處理這些信號。那么,時鐘信號和地址同時到達接收端,波形的對應關(guān)系是什么樣的呢?我們通過仿真來看一下具體波形。 建立如下通道,分別模擬DDR3的地址信號與時鐘信號。

- 關(guān)鍵字: DDR 布線

基于MIMO技術(shù)的視頻緩存器設計方案

- 隨著高速處理器的不斷發(fā)展,嵌入式系統(tǒng)應用的領(lǐng)域越來越廣泛,高速大容量緩存器被廣泛應用于音視頻系統(tǒng)中,然而專用的高速大容量緩存芯片價格過于昂貴,傳統(tǒng)SDRAM在帶寬上已經(jīng)逐漸無法滿足應用.

- 關(guān)鍵字: MIMO技術(shù) 視頻緩存器 DDR

designware ddr介紹

您好,目前還沒有人創(chuàng)建詞條designware ddr!

歡迎您創(chuàng)建該詞條,闡述對designware ddr的理解,并與今后在此搜索designware ddr的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對designware ddr的理解,并與今后在此搜索designware ddr的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司