- 該便攜式接觸網故障信號分析儀采用圖形化程序設計語言LabVIEW開發設計, 可實現數據的高速實時采集、在線分析、自動存儲、顯示等功能。高速數字化儀NI PXI- 5112卡采樣速度高、性能穩定可靠, 適宜對高速變化信號的實時監測。將軟件安裝在PXI- 1042工控機上, 具有體積小、抗干擾能力強、攜帶方便等特點, 同時具有故障性質判斷、故障定位功能。該系統目前已經在石家莊變電所現場運行, 效果良好。

- 關鍵字:

FPGA 8051 TCP IP

- 摘要 在分析Sony公司ICX098BQ面陣CCD圖像傳感器驅動時序的基礎上,對可調節曝光時間的CCD時序發生器及其硬件電路進行設計。選用FPGA器件作為硬件設計平臺,使用VHDL語言對時序關系進行了硬件描述。采用QuartusII 8.0

- 關鍵字:

FPGA CCD 面陣 發生器

- 隨著通信與網絡技術的不斷發展,使我國用現有的E1資源來傳輸以太網業務成為廣泛的應用。以太網數據要通過E1線路傳輸就必須對以太網凈荷數據進行幀封裝,才能從E1線路上恢復出以太網數據幀,完成以太網數據的交換。通常,以太網數據是通過HDLC協議或GFP協議來進行封裝的。本文介紹了中國移動標準協議轉換器中以太網到單路E1轉換器HDLC協議封裝的FPGA(現場可編程邏輯陣列)設計與實現。

- 關鍵字:

中國移動 FPGA 201106

- 摘要 基于Flash存儲器的Hamming編碼原理,在Altera QuartusⅡ7.0開發環境下,實現ECC校驗功能。測試結果表明,該程序可實現每256 Byte數據生成3 Byte的ECC校驗數據,能夠檢測出1 bit錯誤和2 bit錯誤,對于1 bit錯誤

- 關鍵字:

Flash FPGA NAND ECC

- 隨著半導體工藝技術的迅猛發展,現場可編程邏輯器件FPGA的集成度迅速提高,已達到百萬門量級,與此同時,FPGA中的邏 ...

- 關鍵字:

ARM FPGA 加載配置

- 摘要:提出一種通過兩個二階節級聯構成四階IIR數字橢圓濾波器的設計方法,并利用Matlab仿真軟件設計了通帶內波紋不大于0.1 dB,阻帶衰減不小于42 dB的IIR數字濾波器。論述了一種采用可編程邏輯器件,通過VHDL硬件描

- 關鍵字:

Matlab FPGA IIR 數字濾波器

- 在現代數字通信中,對數據傳輸容量和傳輸效率的要求越來越高,因此經常依據時分復用[1]的原理通過數字復接與分...

- 關鍵字:

數字復接技術 FPGA 時分復用

- 摘要:在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘、多級邏輯時鐘和波動式時鐘。

- 關鍵字:

FPGA 時鐘設計

- 1 引 言 在雷達及聲納信號處理系統中,波束形成算法通常采用DSP軟件編程實現,控制邏輯電路采用CPLD來完成,這種方法具有軟件編程靈活、功能易于擴展的優點,但對于實時性能要求很高的系統,如雷達、聲納探測和

- 關鍵字:

FPGA 自適應波束 算法

- 針對高清圖像在中值濾波預處理過程中排序量多、速度慢的特點,提出適合鄰域圖像并行處理機的分塊存儲方法。在流水線結構下,1個時鐘周期可以并行處理32個3×3鄰域的中值濾波運算,實現了高速、實時的1 920×1 080灰度圖像中值濾波器。

- 關鍵字:

FPGA 中值濾波 硬件實現

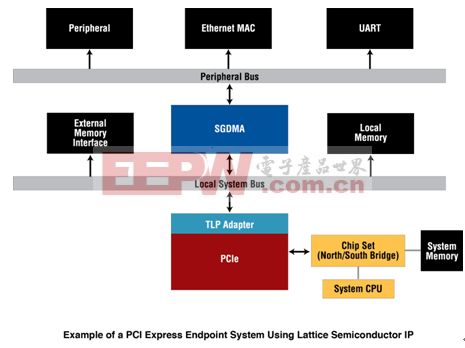

- 萊迪思半導體公司日前宣布LatticeECP3TMFPGA系列符合PCI Express 2.0在2.5Gbps的規范。針對最近PCI – SIG研討會上涉及的1-通道和 4-通道配置,LatticeECP3 FPGA和其PCI Express(PCIe)IP核通過了符合PCI - SIGPCIe 2.0規范和互操作性的測試,確保萊迪思的解決方案與現有的支持系統的PCIe 2.0具有互操作性。

- 關鍵字:

萊迪思 FPGA

- 全球可編程平臺領導廠商賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布榮膺中國經濟CEO論壇“2011中國經濟-最佳推動力企業”獎。賽靈思公司全球高級副總裁、亞太地區執行總裁湯立人(Vincent Tong)和亞太地區銷售與市場副總裁楊飛先生,出席了由東方企業家、經理人雜志、新民周刊、金融界、北京電視臺、香港科技大學商學院、中國企業國際發展協會聯合在北京發起主辦的 “中國經濟CEO論壇暨中國經濟成就獎評選頒獎盛典”。 商務部國際貿易經濟合作研究院研究員白明代表中國經濟CEO 論壇

- 關鍵字:

賽靈思 FPGA

- 萊迪思半導體公司(NASDAQ: LSCC)今日宣布LatticeECP3TMFPGA系列符合PCI Express 2.0在2.5Gbps的規范。針對最近PCI – SIG研討會上涉及的1-通道和 4-通道配置,LatticeECP3 FPGA和其PCI Express(PCIe)IP核通過了符合PCI - SIGPCIe 2.0規范和互操作性的測試,確保萊迪思的解決方案與現有的支持系統的PCIe 2.0具有互操作性。

- 關鍵字:

萊迪思半導體 FPGA

- 0引言傳統的數據采集系統一般采用單片機,系統大多通過PCI總線完成數據的傳輸。其缺點是數學運算能力差...

- 關鍵字:

CPLD FPGA 數據采集系統

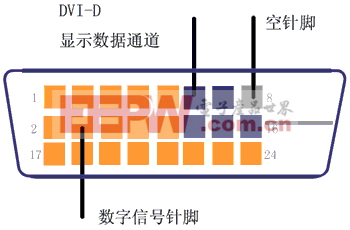

- 一種基于FPGA控制全彩大屏幕顯示的設計,隨著數字技術的飛速發展,各種數字顯示屏也隨即涌現出來有LED、LCD、DLP等,各種數字大屏幕的控制系統多種多樣,有用ARM+FPGA脫機控制系統,也有用PC+DVI接口解碼芯片+FPGA芯片聯機控制系統,在這里我們講述一種不僅

- 關鍵字:

顯示 設計 大屏幕 全彩 FPGA 控制 基于

fpga 介紹

FPGA是英文Field-Programmable Gate Array的縮寫,即現場可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個新概念,內部包括可 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473