基于FPGA的NAND Flash ECC校驗

摘要 基于Flash存儲器的Hamming編碼原理,在Altera QuartusⅡ7.0開發環境下,實現ECC校驗功能。測試結果表明,該程序可實現每256 Byte數據生成3 Byte的ECC校驗數據,能夠檢測出1 bit錯誤和2 bit錯誤,對于1 bit錯誤還能找出其出錯位置并予以糾正,可應用于NAND Flash讀寫控制器的FPGA設計,保證數據傳輸的可靠性。

關鍵詞 ECC校驗;FPGA;NAND Flash;讀寫控制器

移動產品應用領域,NAND Flash設備已成為人們解決高密度固態存儲的專用方法。信息技術的飛速發展,人們對信息的需求量也越來越大。因此,大量數據在系統內部以及網絡之間存儲和傳遞時,對數據進行檢測并更正可能出現的錯誤尤為重要。糾錯碼ECC(Error Correct-ion Code)滿足這一需求,其被稱為ECC校驗,是一種常用于NAND Flash讀寫控制器的校驗編碼。

ECC校驗負責檢測錯誤、維護ECC信息、更正由原數值改變了的單比特錯誤。所有ECC的操作處理都可由一個ECC模塊來控制,其作為一種簡單地存儲一映射接口,放置在NAND器件和處理器接口之間。該模塊一般包含Hamming編碼產生模塊和出錯位置模塊,分別用于產生ECC校驗碼和計算出錯位置。

1 Haremina編碼

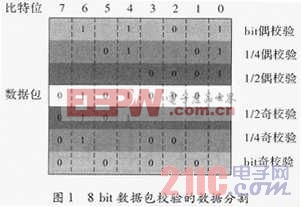

Hamming編碼計算簡單。廣泛用于NAND Flash的Hamming算法,通過計算塊上數據包得到2個ECC值。為計算ECC值,數據包中的比特數據要先進行分割,如1/2組、1/4組、1/8組等,直到其精度達到單個比特為止,以8 bit即1 Byte的數據包為例進行說明,如圖1所示。

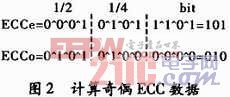

該數據按圖1所示方式進行比特分割,分別得到上方的偶校驗值ECCe和下方的奇校驗值ECCo。其中,1/2校驗值經“異或”操作構成ECC校驗的最高有效位,同理1/4校驗值構成ECC校驗的次高有效位,最低有效位由具體到比特的校驗值填補。圖2展示了兩個ECC校驗值的計算過程。

即偶校驗值ECCe為“101”,奇校驗值ECCo為“010”。圖1所示為只有1 Byte數據的數據包,更大的數據包需要更多的ECC值。事實上,每n bit的ECC數值可滿足2nbit數據包的校驗要求。又由于這種Hamming碼算法要求一對ECC數據(奇偶),所以總共要求2n bit的ECC校驗數據來處理2nbit的數據包。

計算之后,原數據包和ECC數值都要寫入NAND器件。稍后,原數據包將從NAND器件中讀取,此時ECC值將重新計算。如果新計算的ECC不同于先前編入NAND器件的ECC,那么表明數據在讀寫過程中出錯。

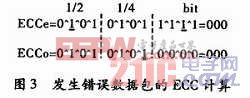

例如,原始數據01010001中有1個單一的比特出現錯誤,出錯后的數據是01010101。經前面所示方法計算,從圖3中可以清楚地看到由于數據發生了變化,2個新的ECC數值已不同與原來的ECC值。

評論