基于FPGA的NAND Flash ECC校驗

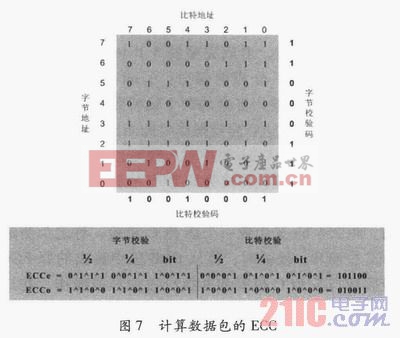

當數據包發生錯誤時,錯誤檢測和更正所使用的方法與先前所描述的方法相似,這里仍以1 bit錯誤來說明校驗過程,具體如圖8所示。

經步驟1~步驟4的計算,新的數據包存在錯誤且出錯位置為“110010”,由于前面將字節校驗碼設為ECC值的高位,比特校驗碼設為低位,因此,“110010”的高有效位表示出錯的字節地址,低有效位代表出錯的比特地址,即字節地址為6、比特地址為2的數據發生了錯誤,與設定的錯誤情況相符。此時,只需將該位的數據比特與“1”異或即可完成數據包的修正。

將8 Byte數據包擴展到512 Byte數據包,雖然數據量大大增加,但僅添加了數據分割的情況,算法仍然一樣。計算所得奇偶ECC數據均為12 bit長,其中,3個低有效位代表bit地址(7~0),9個高有效位代表512Byte的地址(255~0)。

3 實驗分析

本實驗處理對像為256 Byte的數據包,對其進行ECC校驗共生成22 bit校驗數據。為方便讀取,可以在末尾添加兩位,形成完整的3Byte校驗數據。這3 Byte共24 bit,分成兩部分:6 bit的比特校驗和16 bit的字節校驗,多余的兩個比特置1并置于校驗碼的最低位,在進行異或操作時此兩比特忽略。

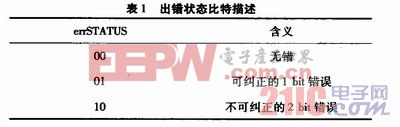

當往NAND Flash頁中寫人數據時,每256 bit生成一個ECC校驗,稱之為原ECC校驗和,并保存到頁的OOB數據區中;當從NAND Flash中讀取數據的時,每256 bit又生成一個新ECC校驗,稱之為新的ECC校驗和。校驗時,將從OOB區中讀出的原ECC校驗和與新ECC校驗和并執行按位異或操作,若計算結果為全“0”,則表示不存在出錯,并將出錯狀態變量errSTATUS賦值為“00”;若結果為全“1”,表示出現1個比特錯誤,將errSTATUS賦值為01”并進行糾正;除全“0”和全“1”外的其他情況將errSTATUS賦值為“10”表示出現了無法糾正的2 bit錯誤,如表1所示。

實驗仿真環境為Altera Quartus II 7.0,編程語言為VHDL。VHDL語言為硬件編程語言,具有并行處理的特點,而原程序中有大量的需要并行處理的異或操作,因此程序執行效率高,非常有利于硬件實現。

評論