- 為設計一個項目可用的FIR數字帶通濾波器,采用Matlab/Simulink軟件中DSPBulider強大的算法模塊設計工具,結合Altera公司的FPGA開發板實現FIR數字帶通濾波器的系統集成、RTL級仿真、綜合編譯、下載等設計流程,并對正弦信號進行濾波,結果下載到開發板上用示波器觀測,達到了預期的濾波效果和目的。基于DSPBuilder完成系統建模,省去了復雜的VHDL編程,還可針對具體模塊進行參數設置從而適應不同的濾波需求。該方法實現簡單、可靠,還可類推實現其他復雜的嵌入式系統設計。

- 關鍵字:

FPGA FIR 帶通濾波器

- 0 引 言

根升余弦成形濾波器是數字信號處理中的重要部件,它能對數字信號進行成形濾波,壓縮旁瓣,減少干擾的影響,從而降低誤碼率。根據文獻[1],它的傳統FP-GA實現方式基于乘累加器(Multiplier Add Cell,M

- 關鍵字:

FPGA 多速率 濾波器

- 該設計利用FPGA的嵌入式軟核NiosⅡ處理器,通過嵌入式操作系統μC/OS-Ⅱ,實現了在FPGA內的自相關計算器;利用FPGA強大的并行運算功能和自帶存儲器實現的“乒乓”RAM,通過軟核NiosⅡ輸出控制字實時切換調用兩個“乒乓”RAM的存儲和讀取功能,使之同時完成對采集數據的緩沖存儲和向乘法器提供計算數據的功能,使芯片的整個數字處理鏈路連續化。另外,采用多比特進行自相關運算較之于現在天文臺使用的1 b量化自相關器,能有效地提高SNR退化比。

- 關鍵字:

FPGA 嵌入式 比特

- 0 引 言

PC/104嵌入式控制PC出現于20世紀80年代末,并于1992年形成IEEEP966.1標準。它一方面繼承了PC的所有資源,另一方面又對PC的各個方面做了優化設計,使其與IBM PC完全兼容,并具有體積小,功耗低,工作

- 關鍵字:

FPGA 104 CAN 通訊板

- 0 引 言

眾所周知,在二元域、有限域以及復數域都不存在理想的地址碼,如m序列、Gold序列以及Walsh碼的相關性都不理想,這使得采用傳統擴頻碼的CDMA系統是一個自干擾系統,需要采用聯合檢測技術、智能天線技術

- 關鍵字:

FPGA LS碼

- 0 引 言

以大氣作為傳輸介質,激光作為信息載體進行無線通信時,空一地激光無線通信是激光無線通信的一種常見形式,信標光的準確捕獲、瞄準與跟蹤(Acquisition,Pointing and Tracking,APT)是其關鍵技術,AP

- 關鍵字:

FPGA 激光 跟蹤系統 無線通信

- 要點經濟形勢刺激了對可編程模擬元件的興趣。不存在將可編程模擬芯片用于一個系統的設計流程...

- 關鍵字:

FPGA 可編程邏輯 解決方案

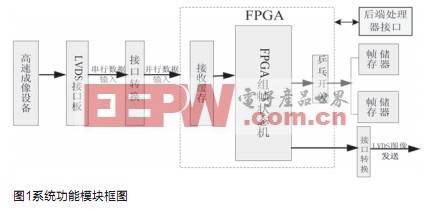

- 本文介紹了一種基于FPGA實現的圖像采集系統,通過FPGA控制外部高速成像設備所產生的圖像數據、參數信息和狀態控制信號的同步采集,并實現數據格式的轉換、圖像數據的組幀、存儲及轉發功能。

- 關鍵字:

FPGA 圖像采集 組幀狀態機 LVDS 200911

- 可編程邏輯器件(FPGA)一直以其設計靈活性以及現場可編程特性在市場上穩穩固守著一席之地,隨著半導體制造工藝的進步,器件集成度越來越高,其應用也日益復雜。過去FPGA應用對象主要是硬件設計人員,他們對器件本身的物理結構及特性都有相當的了解,而如今系統集成工程師、DSP開發人員甚至嵌入式軟件工程師也都需要在可編程邏輯器件平臺上進行系統開發,FPGA器件的復雜性對他們將是一大挑戰。

“目前的FPGA已經和以前有很大不同,過去它只包含幾千個查找表用于膠合邏輯,僅僅作為嵌入式系統中的器件,而

- 關鍵字:

FPGA DSP

- Avago Technologies(安華高科技)今日宣布,公司提供的關鍵知識產權(IP, Intellectual Property)已經幫助Juniper Networks公司成功進行高性能硅芯片器件產品的開發,這些新設計為帶來Juniper公司MX-3D平臺Junos® Trio芯片組的一部分。Avago為提供通信、工業和消費性等應用模擬接口元器件之全球領導廠商。

每個器件都擁有接近100個SerDes串行/解串器通道,并且可以推動松散背板通道和多重背板連接器,除了展現出同級產品最

- 關鍵字:

Avago 硅芯片 IP

- Turbo碼是由法國人Berrou于1993年提出的一種性能優越的信道編碼方案[1],其應用已逐步推廣到衛星通信、移動通信和計算機通信等領域。交織器作為Turbo碼編碼器中的重要組成部分,在Turbo碼的性能中起著至關重要

- 關鍵字:

FPGA 改進型 分組 交織器

- Altera公司今天宣布推出Quartus® II軟件9.1——在CPLD、FPGA和HardCopy® ASIC設計方面,業界性能和效能最好的軟件。與以前的軟件版本相比,Quartus II軟件9.1新特性和增強功能將編譯時間縮短了20%,編譯時間比競爭高密度40-nm和65-nm設計仍然快2到3倍。軟件新特性是快速重新編譯,對于較小的設計改動,這一特性大大縮短了編譯時間,而且還支持Altera最新發布的Cyclone®IV FPGA。

Quar

- 關鍵字:

Altera Quartus CPLD FPGA HardCopy

fpga ip介紹

您好,目前還沒有人創建詞條fpga ip!

歡迎您創建該詞條,闡述對fpga ip的理解,并與今后在此搜索fpga ip的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473