EEPW首頁(yè) >>

主題列表 >>

fpga+dsp

fpga+dsp 文章 最新資訊

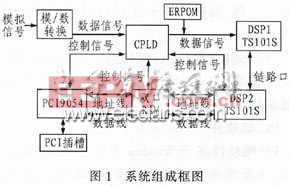

基于CY7C68013A和FPGA的ADSP-TS101擴(kuò)展USB接口設(shè)計(jì)

- 基于CY7C68013A和FPGA的ADSP-TS101擴(kuò)展USB接口設(shè)計(jì),ADI公司的DSP器件(ADSP-TS101)具有浮點(diǎn)實(shí)時(shí)處理能力強(qiáng)、并行性好等優(yōu)點(diǎn),從而廣泛被彈載信號(hào)處理系統(tǒng)選用。其作為彈載主處理器,在導(dǎo)彈的系統(tǒng)試驗(yàn)中,需要利用上位機(jī)對(duì)其中的大數(shù)據(jù)量的軟件變量進(jìn)行實(shí)時(shí)監(jiān)控和記錄,

- 關(guān)鍵字: USB 接口 設(shè)計(jì) 擴(kuò)展 ADSP-TS101 CY7C68013A FPGA 基于

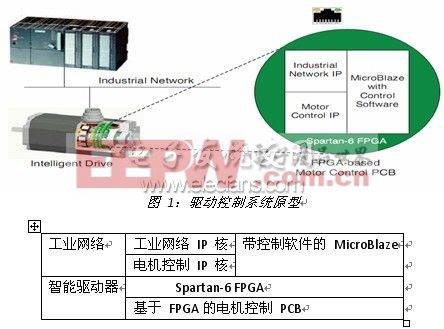

基于Spartan-6 FPGA的可擴(kuò)展驅(qū)動(dòng)控制系統(tǒng)

- 基于Spartan-6 FPGA的可擴(kuò)展驅(qū)動(dòng)控制系統(tǒng),許多情況下驅(qū)動(dòng)器只是大規(guī)模工藝的一個(gè)組件,因此互操作性也是一項(xiàng)關(guān)鍵的設(shè)計(jì)要求。而影響這種要求的關(guān)鍵因素是工業(yè)網(wǎng)絡(luò)協(xié)議的寬度(即現(xiàn)場(chǎng)總線)和相關(guān)器件特性,因?yàn)樗鼈冇脕?lái)標(biāo)準(zhǔn)化驅(qū)動(dòng)器在網(wǎng)絡(luò)中的表達(dá)。現(xiàn)場(chǎng)總線(比

- 關(guān)鍵字: 驅(qū)動(dòng) 控制系統(tǒng) 擴(kuò)展 FPGA Spartan-6 基于

DSP系統(tǒng)的動(dòng)態(tài)加載技術(shù)研究

- DSP系統(tǒng)的動(dòng)態(tài)加載技術(shù)研究,目前,開(kāi)發(fā)人員發(fā)現(xiàn)動(dòng)態(tài)加載應(yīng)用模塊是在運(yùn)行期間再配置系統(tǒng)以改變或擴(kuò)展其功能的最有效方式。開(kāi)發(fā)人員不能 在運(yùn)行前靜態(tài)配置許多 DSP 系統(tǒng),其原因在于執(zhí)行操作的實(shí)時(shí)要求。但是,動(dòng)態(tài)加載允許系統(tǒng)根據(jù)需要進(jìn)行自身

- 關(guān)鍵字: 技術(shù) 研究 加載 動(dòng)態(tài) 系統(tǒng) DSP

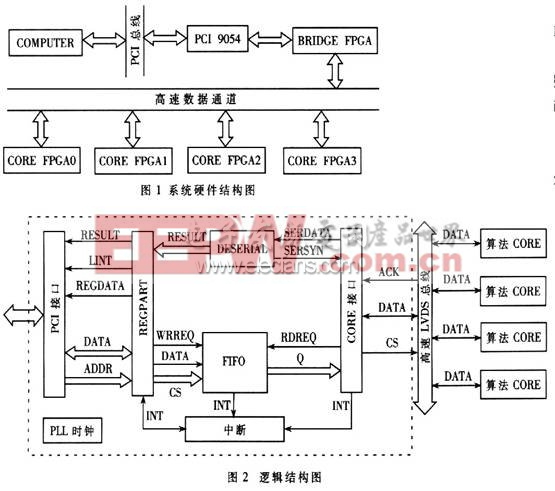

基于FPGA PCI的并行計(jì)算平臺(tái)實(shí)

- 基于FPGA PCI的并行計(jì)算平臺(tái)實(shí),本文介紹的基于PCI總線的FPGA計(jì)算平臺(tái)的系統(tǒng)實(shí)現(xiàn):通過(guò)在PC機(jī)上插入擴(kuò)展PCI卡,對(duì)算法進(jìn)行針對(duì)并行運(yùn)算的設(shè)計(jì),提升普通PC機(jī)對(duì)大計(jì)算量數(shù)字信號(hào)的處理速度。本設(shè)計(jì)采用5片F(xiàn)PGA芯片及相關(guān)周邊芯片設(shè)計(jì)實(shí)現(xiàn)這一并行高速

- 關(guān)鍵字: 計(jì)算 平臺(tái) 并行 PCI FPGA 基于

基于DSP的PCI總線數(shù)據(jù)采集系統(tǒng)研究

- 本文以實(shí)際開(kāi)發(fā)系統(tǒng)為背景,以TI公司的TMS320VC5402與PLX公司的PCI9052為基礎(chǔ)。詳細(xì)論述了基于DSP的PCI總線結(jié)構(gòu)的數(shù)據(jù)采集系統(tǒng)硬件及軟件設(shè)計(jì)方案和實(shí)現(xiàn)方法。

- 關(guān)鍵字: DSP PCI 總線 數(shù)據(jù)采集

NEC推出大規(guī)模集成電路設(shè)計(jì)工具CyberWorkBench

- 近日,NEC 推出了半導(dǎo)體設(shè)計(jì)高階綜合工具CyberWorkBench的FPGA專用版。CyberWorkBench是NEC開(kāi)發(fā)的以C語(yǔ)言為基礎(chǔ)的LSI(注1)設(shè)計(jì)工具。該工具以ANSI-C、SystemC等C語(yǔ)言程序作為輸入,以自動(dòng)生成高性能和高質(zhì)量的電路的合成工具為中心,具備與軟件協(xié)調(diào)的高速驗(yàn)證環(huán)境、源碼調(diào)試功能、形式屬性驗(yàn)證等豐富的驗(yàn)證功能,從而實(shí)現(xiàn) All-in-C 。通常在設(shè)計(jì)LSI時(shí),要使用硬件專用的描述語(yǔ)言HDL(注2),而使用CyberWorkBench,由于可以輸入C語(yǔ)言,從而使設(shè)計(jì)描述

- 關(guān)鍵字: NEC FPGA

fpga+dsp介紹

您好,目前還沒(méi)有人創(chuàng)建詞條fpga+dsp!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司