- 摘要:在科技飛速發展的今天,各種自動化儀器及自動控制都離不開信號采集,而且要采集的信號越來越快,精度要求也越來越高。如何簡單快速的讓系統集成這項功能呢?

1、ZSDA1000的基本介紹 ZDS1000是ZLG致遠電子開發的高速信號數據采集模塊,模塊通過PCI Express2.0接口與主機端連接,350M帶寬,1GSa/s的采樣速率。用戶只需要通過動態鏈接庫文件就可以輕松控制模塊進行數據采集和數據處理。可用于質譜分析、雷達信號捕捉、材料分析等場

- 關鍵字:

FPGA ZSDA1000

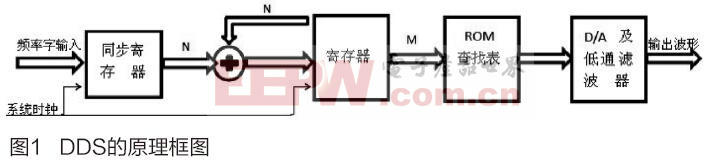

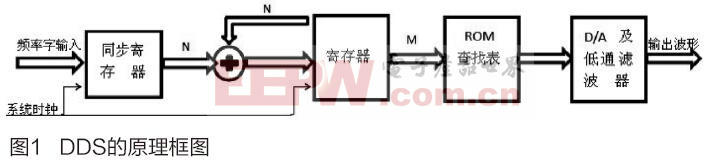

- 本文利用直接數字合成技術通過一款FPGA可編程邏輯芯片實現函數信號發生器的研制,該信號發生器是以Altera公司生產的EP4CE6F17C8芯片為設計載體,通過DDS技術實現兩路同步信號輸出。通過軟件Quartus-II12.0和Nios-II 12.0開發環境編程,實現多種波形信號輸出,信號具有高精度的頻率分辨率能力,最高可達36位。最后通過實驗輸出的波形信號符合標準。

- 關鍵字:

直接數字合成技術 FPGA 信號發生器 Quartus-II 201512

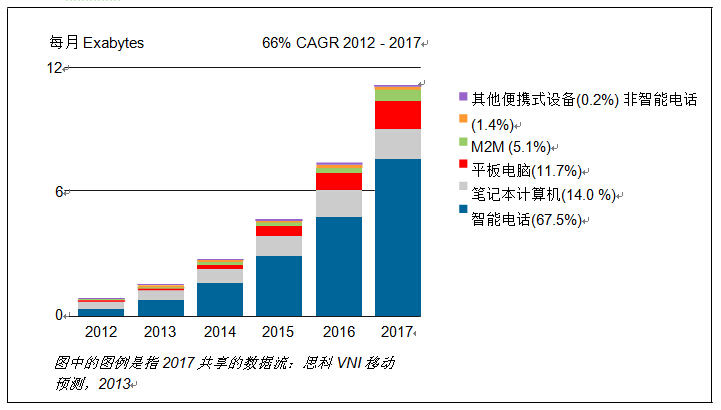

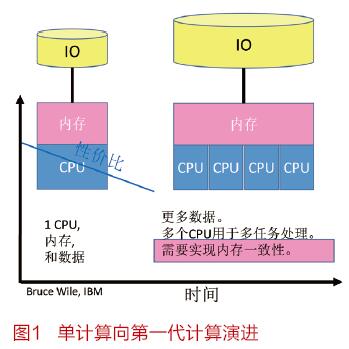

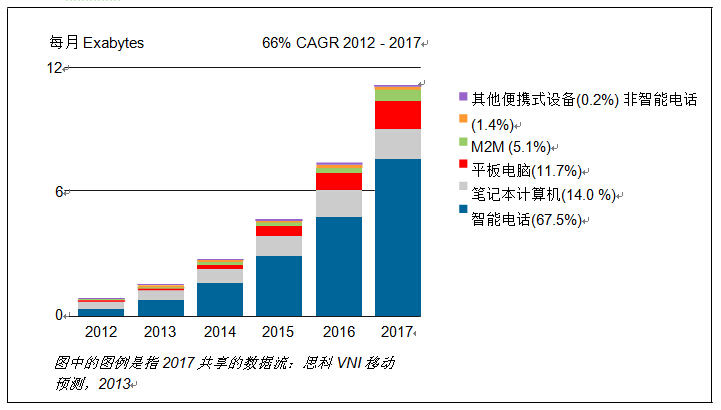

- 本白皮書介紹為什么電信帶寬和基礎設施促進了FPGA功能的增強,以及ASIC和ASSP面臨的商業挑戰,可編程邏輯器件(PLD)定制方法是怎樣支持FPGA功能的跨越式發展。本文還簡要介紹了下一代FPGA和SoC系列品。 引言 最新發布的FPGA是硬件規劃人員、軟件開發人員和系統設計人員實現其下一代產品目標的關鍵支撐因素。大量的電信基礎設施成指數增長的帶寬需求以及各行業使用這些帶寬的需求使得現有硬件和軟件解決方案很難滿足性能要求,也難以達到成本和功耗目標。ASIC、ASSP和獨立處理器遇到了發展瓶頸,P

- 關鍵字:

FPGA SoC

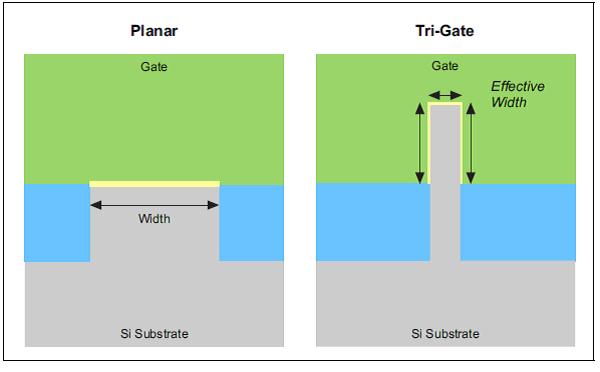

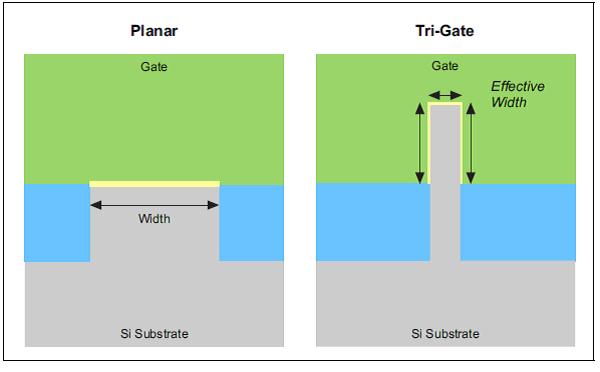

- 引言 2013年2月,Altera公司與Intel公司共同宣布了Altera下一代最高性能FPGA產品的生產將獨家采用Intel的14nm 3D Tri-Gate(三柵極)晶體管技術。這使得Altera成為當前采用最先進、最高性能半導體技術的獨家專業FPGA供應商。本文介紹了三柵極及相關技術的歷史與現狀,以便了解三柵極技術對高性能FPGA性能的影響,以及其在數字電路速度、功率以及生產方面有何種程度的優勢。 晶體管設計的背景 1947年,貝爾實驗室展示了第一支晶體管,采用的是鍺

- 關鍵字:

Altera FPGA

- Altera公司今天宣布,開始提供面向Nios? II嵌入式處理器的Altera?功能安全鎖步解決方案,這一解決方案降低了設計周期風險,幫助系統設計人員簡化工業和汽車安全應用的認證。Altera與意大利比薩的功能安全領先供應商YOGITECH聯合開發的鎖步解決方案采用了Altera FPGA、SoC,認證工具流程,以及YOGITECH的知識產權(IP)內核。這一解決方案幫助客戶在Altera FPGA中輕松實現SIL3安全設計,包括低成本Cyclone? V&n

- 關鍵字:

Altera FPGA

- 面對清華紫光集團董事長趙偉國再次放話,將先把收購目光集中在美國半導體產業的說法,日前臺系IC設計公司均表達不意外,畢竟臺灣政府目前尚未通過相關法令限制,加上相關配套措施還需產官學界互相討論,與其現在買市值不大的臺灣IC設計公司,對清華紫光集團并無法產生立即性的幫助。

產業界人士指出,以清華紫光的大陸內需市場色彩,加上先前出手目標多鎖定具備一定程度寡占特性的產業來看,全球三強鼎立的EDA市場、繪圖芯片與FPGA產業,或許是清華紫光集團在談判桌上的下一個目標。

確實從清華紫光收購動作一路多鎖定

- 關鍵字:

紫光 FPGA

- Altera公司(Nasdaq)公開業界第一款異構系統級封裝(SiP,System-in-Package)器件,集成了來自SK Hynix的堆疊寬帶存儲器(HBM2)以及高性能Stratix® 10 FPGA和SoC。Stratix 10 DRAM SiP代表了新一類器件,其特殊的體系結構設計滿足了高性能系統對存儲器帶寬最嚴格的要求。

數據中心、廣播、固網和高性能計算等系統要處理的數據量不斷攀升,需要的帶寬非常高。相對于目前的分立DRAM解決方案,Stratix 10 DRAM SiP的

- 關鍵字:

Altera FPGA

- Altera公司今天公開業界第一款異構系統級封裝(SiP,System-in-Package)器件,集成了來自SK Hynix的堆疊寬帶存儲器(HBM2)以及高性能Stratix® 10 FPGA和SoC。Stratix 10 DRAM SiP代表了新一類器件,其特殊的體系結構設計滿足了高性能系統對存儲器帶寬最嚴格的要求。

數據中心、廣播、固網和高性能計算等系統要處理的數據量不斷攀升,需要的帶寬非常高。相對于目前的分立DRAM解決方案,Stratix 10 DRAM SiP的存儲器帶寬提

- 關鍵字:

Altera FPGA

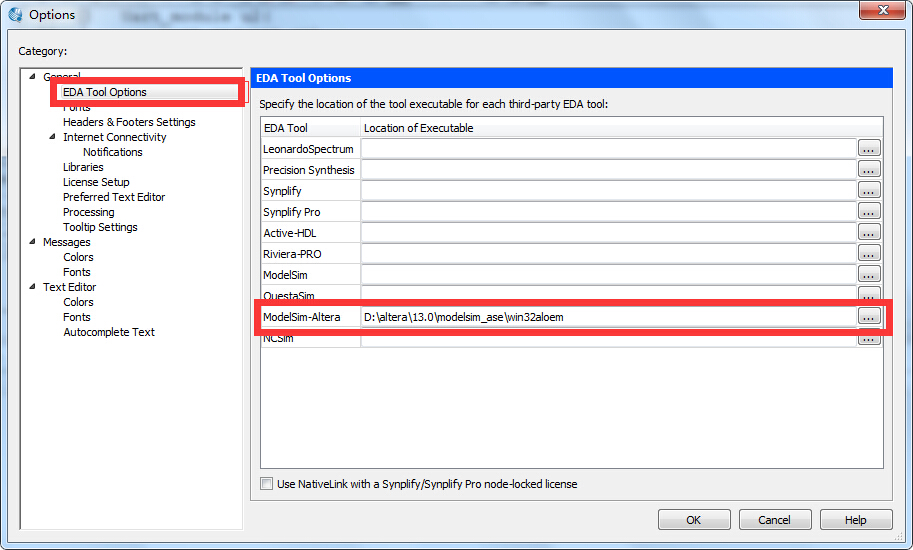

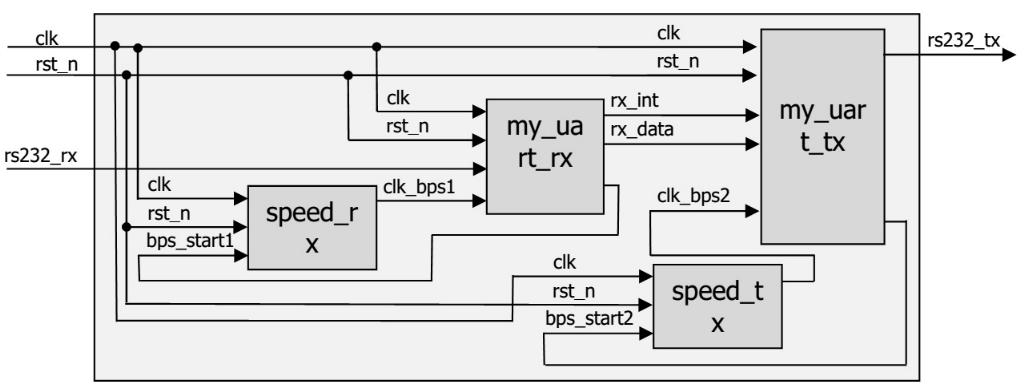

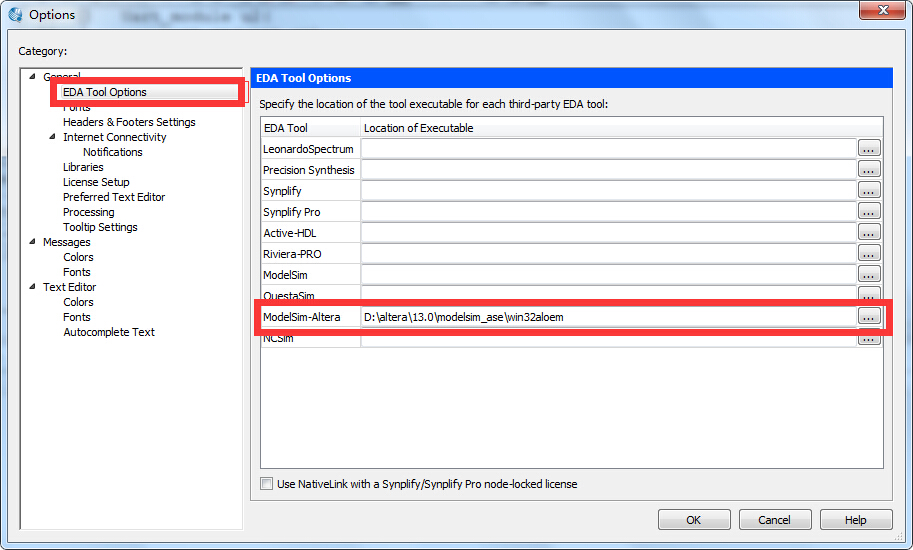

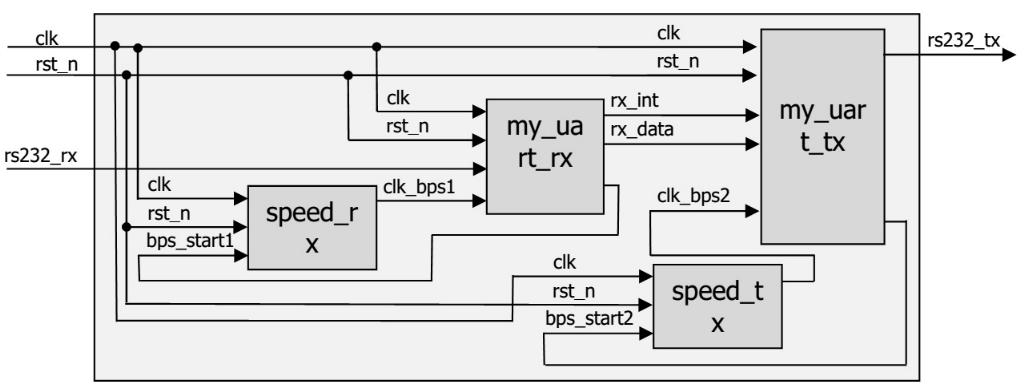

- 以上為小梅哥為了對特權同學的串口收發模塊進行測試所展開的部分工作,到這里,仿真測試所需要的準備工作我們就做好了,接下來將實際進行仿真,通過仿真來分析該模塊的性能。 這里極力推薦大家使用modelsim進行仿真,因為quartusII自帶的仿真工具靈活性和功能都趕modelsim相差甚遠。Modelsim作為一款強大的仿真軟件,在業界被廣泛使用。同時,modelsim針對不同的EDA廠家,也推出了OEM版本,modelsim-altera就是為Altera公司開發的OEM版本,此版本針對Altera公

- 關鍵字:

FPGA 串口調試

- 大家好,這幾天在各個論壇上,經常就有人在向我咨詢基于FPGA的串口通信代碼,大部分都是在網上下載一個現成的代碼,但是在使用中就遇到了各種問題,于是就發到了論壇上來求助。在閱讀了他們的代碼之后,我發現幾乎出自同一個版本(目前確定為特權同學的基于EPM240入門實驗的代碼)。他們在調試這個代碼的時候,經常存在這樣幾個問題:1、部分人對該串口通訊模塊完全不理解,對每句話,甚至每個模塊的功能都不理解;2、部分人采用最原始的畫波形的方式來對該模塊進行仿真,結果無法得到仿真結果;3、部分人不會使用modelsim

- 關鍵字:

FPGA 串口調試

- “數十個合作伙伴,數百家客戶,數千計的工程師,這三股強大的力量構成了Altera SoC大的生態系統,也是Altera在SoC領域投入5年所獲得的成就。”Altera公司嵌入式處理營銷資深總監Chris Balough在一年一度的Altera SoC開發者大會上自豪地表示。

- 關鍵字:

Altera FPGA

- 消費類電子產品經過幾十年的發展已經有無數種各類用途的設備,從專業設備到個人消費品。雖然存在性能和功能的差異,但是消費類電子產品往往遵循相同 的設計趨勢:設備功能變得越來越強大、體積小巧和省電。可穿戴設備集中體現了這一趨勢,它是一種便攜、電池供電、高集成度的設備,負責從高精度模擬測量到 直觀用戶界面的所有一切。可穿戴式設備開發人員必須仔細的在多種集成電路(IC)中匹配產品的需求,有時還需要同時應對相互矛盾的優先選項。 例 如,讓我們仔細思考,在靈巧的可穿戴式設計中如何兼顧

- 關鍵字:

MCU 可穿戴

- Altera公司榮獲分析公司Frost & Sullivan的全球FPGA技術創新領先獎,表彰Altera在技術特性和未來業務價值方面更勝一籌。該獎項彰顯Altera在其Arria® 10 FPGA中實現IEEE 754單精度硬核浮點DSP (數字信號處理)模塊——處理速率高達1.5 TFLOPS (每秒萬億次浮點運算),進一步提高了數字系統設計的能效和生產效率。Altera的可編程器件幫助客戶針對大數據和搜索應用、數據中心加速、軍事通信和高性能計算等需要高精度

- 關鍵字:

Altera FPGA

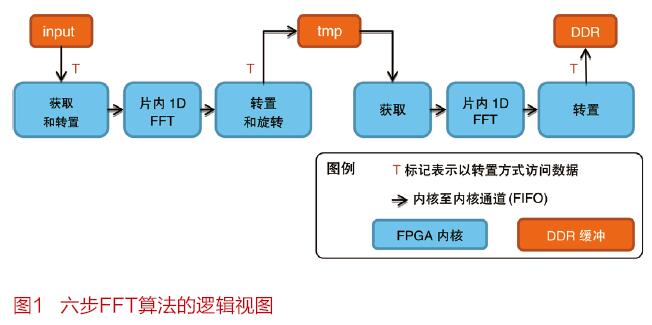

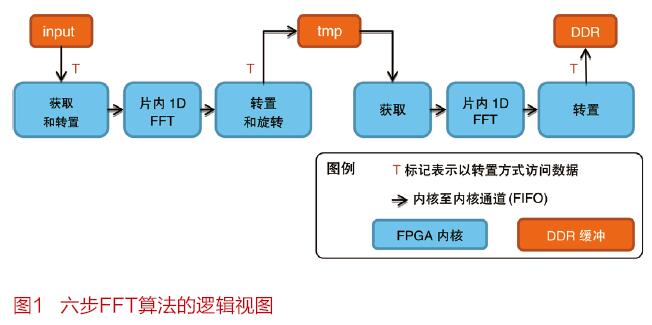

- 快速傅里葉變換(FFT)是信號處理應用的基礎。FPGA供應商一直以來提供了運行良好的FFT庫,處理適配到FPGA片內存儲器中的大量數據。但是,如果數據規模太大,應該如何應對? 為解決這一問題,FPGA設計人員現在必須要做出設計決定,這些決定互相糾纏在一起,例如,片內FFT內核的配置選擇,其數量,它們怎樣連接并訪問外部存儲器,多個內核之間的同步等。分析所有這類設計決定就是要能夠很好的結合現有產品,在HDL中編程,這會非常耗時,而且帶來了性能問題。采用OpenCL等高級編程語言,能夠很快的完成系統設計分析。本

- 關鍵字:

FPGA 頻域濾波器 OpenCL 201511

fpga+mpu+mcu介紹

您好,目前還沒有人創建詞條fpga+mpu+mcu!

歡迎您創建該詞條,闡述對fpga+mpu+mcu的理解,并與今后在此搜索fpga+mpu+mcu的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473