- 基于FPGA的信號發生器設計,以FPGA 芯片為載體, 通過QuartusII 的LPM_ROM 模塊和VHDL 語言為核心設計一個多功能信號發生器,根據輸入信號的選擇可以輸出遞增鋸齒波、遞減鋸齒波、三角波、階梯波和方波等5 種信號,通過QuartusII 軟件進行波形仿

- 關鍵字:

設計 信號發生器 FPGA 基于

- 為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定FIFO深度的方法。對FIFO不同深度的實驗表明,采用該方法設定的FIFO深度能夠

- 關鍵字:

LabVIEW FPGA FIFO 模塊

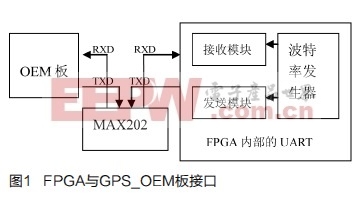

- 本文提出了一種基于FPGA的嵌入式UART模塊化設計方法,通過UART實現了FPGA與GPS_OEM板之間的數據通信。基于VHDL語言,通過有限狀態機,將UART模塊集成到FPGA上,給出了系統的功能仿真結果,驗證了系統設計的正確性,增強了設計的靈活性。

- 關鍵字:

FPGA UART 201109

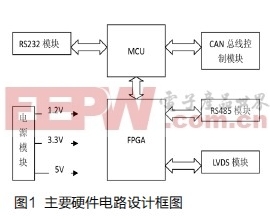

- 設計的航空總線接口板測試平臺滿足通用設備CAN總線、RS485差分電平異步總線及LVDS差分電平異步總線數據傳輸要求。通過對各模塊功能分析,在仿真軟件中通過功能仿真驗證,并在工程應用中得到驗證。此設計通過RS232接口連接上位機實現數據收發,并能對CAN總線及高速異步總線參數進行動態配置。

- 關鍵字:

CAN FPGA MCU 201109

- FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的...

- 關鍵字:

低功耗 FPGA

- 作為基于FPGA原型方法的擁護者,有人可能會認為我們只片面地看到了這種方法的優點,而對其缺陷視而不見。但那...

- 關鍵字:

FPGA 原型設計

- intevac是商用和軍用市場光學產品的前沿開發商。本文介紹該公司nightvista嵌入式電子系統的開發,該產品是高...

- 關鍵字:

可配置軟核處理器 FPGA DSP

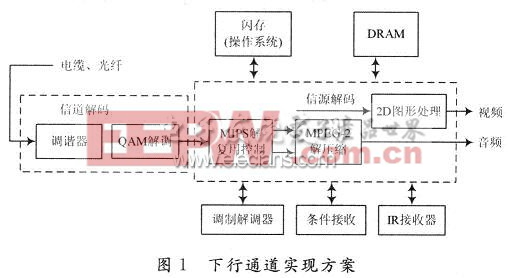

- LEON2應用于DCPU的FPGA仿真,近年來,隨著數字多媒體業務和Internet網絡的迅速發展,新型數字機頂盒可以有效利用我國巨大的有線電視網絡資源,完成視頻點播、數字電視的接收及接入Internet等綜合業務功能。

1 數字機頂盒總體設計方案

- 關鍵字:

仿真 FPGA DCPU 應用 LEON2

- AMD(AMD-US)日前宣布,原任產品事業群總經理Rick Bergman已離開AMD,其職缺將由AMD總裁暨執行長Rory Read暫代其職位,同時AMD也宣布延攬前Comcast資深副總裁Paul Struhsaker,擔任AMD全球副總裁暨商用企業部門總經理,帶領新成立的商用企業部門(Commercial Business Division)。

- 關鍵字:

AMD FPGA

- 基于FPGA的視頻應用OSD設計,近年來,數字視頻監控系統在銀行、高速公路、樓宇等各個領域取得了廣泛的應用。在數字視頻監控系統中,OSD(On Screen Display)技術是不可或缺的部分。OSD為用戶提供友好的人機界面,能夠使用戶獲得更多的附加信息。系

- 關鍵字:

OSD 設計 應用 視頻 FPGA 基于

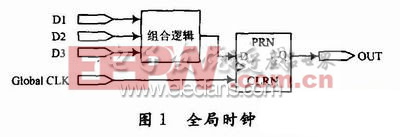

- 基于FPGA的時鐘設計,對于一個設計項目來說,全局時鐘是最簡單和最可預測的時鐘。在PLD/FPGA設計中最好的時鐘方案是由專用的全局時鐘輸入引腳驅動的單個主時鐘去鐘控設計項目中的每一個觸發器。只要可能就應盡量在設計項目中采用全局時鐘

- 關鍵字:

設計 時鐘 FPGA 基于

- 隨著FPGA的密度越來越高,設計者們正在節能降耗方面取得越來越多的進展。出現降低功耗這一趨勢的另一個原因是...

- 關鍵字:

FPGA

- 您編寫的代碼是不是雖然在仿真器中表現正常,但是在現場卻斷斷續續出錯?要不然就是有可能在您使用更高版本的工...

- 關鍵字:

FPGA

fpga-nios介紹

您好,目前還沒有人創建詞條fpga-nios!

歡迎您創建該詞條,闡述對fpga-nios的理解,并與今后在此搜索fpga-nios的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473