mcu-fpga 文章 最新資訊

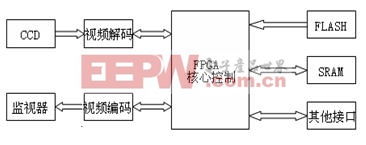

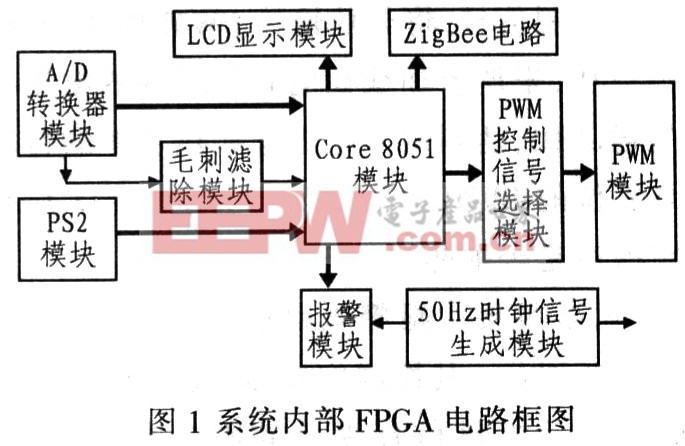

擴散爐溫度自動控制系統(tǒng)中的FPGA設計

- 擴散爐溫度自動監(jiān)控系統(tǒng)是對雙管擴散爐溫控部分進行改造,以提高爐溫精度,從而提高生產(chǎn)線的成品率,降低系統(tǒng)能耗。通過對Actel公司的Fusion系列器件FPGA編程實現(xiàn)系統(tǒng)的硬件控制。用C語言對Actel FPGA內置的8051軟核編程實現(xiàn)系統(tǒng)的軟件控制。整個監(jiān)控系統(tǒng)完成數(shù)據(jù)采集、控制算法和ZigBee無線傳輸?shù)裙δ堋y試表明,采用Fusion FPGA設計.可以同時完成多路溫度控制,整個系統(tǒng)的控制精度也有進一步的提高。

- 關鍵字: FPGA 設計 控制系統(tǒng) 自動 溫度 擴散 轉換器

TI推出實時控制的新型 C2834x Delfino MCU

- 日前,德州儀器 (TI) 宣布推出性能提升兩倍、工作頻率高達 300 MHz 并高度集成了 516KB 單周期存取 RAM 存儲器、高分辨率脈寬調制輸出 (PWM)、32 位 QEP 模塊以及其它控制導向型特性的 TMS320C2834x系列 Delfino 浮點控制器,從而可為高端控制應用提供高性能、高浮點精度以及優(yōu)化的控制外設,以充分滿足系統(tǒng)效率、精度以及可靠性等嚴格的性能要求。新型 Delfino 器件由兩套精心設計的全新模塊化 controlCARD 工具提供支持,可實現(xiàn)伺服驅動、可再生能源、

- 關鍵字: TI,MCU,浮點控制

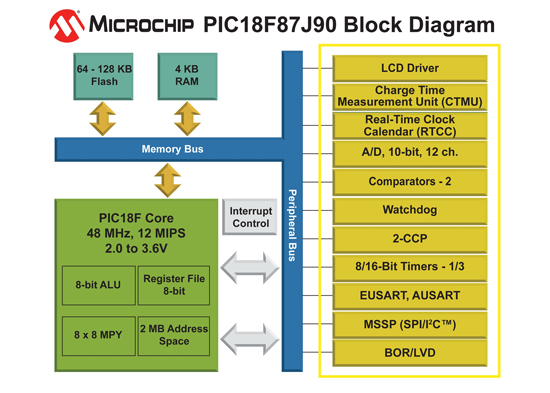

Microchip PIC18F87J90系列擴展8位LCD MCU存儲

- 全球領先的單片機和模擬半導體供應商——Microchip Technology Inc.(美國微芯科技公司)今天宣布推出采用納瓦(nanoWatt)技術的PIC18F87J90 8位LCD直接驅動單片機(MCU)。這些64引腳和80引腳封裝的新器件,擴展了Microchip LCD MCU系列的存儲容量,并提供了更豐富的外設。新器件具備64至128 KB的閃存及4 KB的RAM內存,是業(yè)界首款既備有實時時鐘和日歷(RTCC),又包含容性觸摸傳感或精確時間測量所需的充電時間測量單

- 關鍵字: Microchip,MCU,LCD PIC

FPGA的可重構測控系統(tǒng)應用設計的研究

- 1可重構測控系統(tǒng)的提出測控系統(tǒng)一般是指基于計算機實現(xiàn)數(shù)據(jù)采集和控制的系統(tǒng)。測控系統(tǒng)在工業(yè)現(xiàn)場控制、家...

- 關鍵字: FPGA 測控系統(tǒng) 應用設計

瑞薩攜手EngineLab 成功舉辦汽車電子研討會

- 2009年的1月,瑞薩中國攜手美國EngineLab公司成功在中國重要的汽車產(chǎn)業(yè)城市長春舉辦了針對汽車制造商的汽車電子現(xiàn)場研討會,之后的2月又于蕪湖以CIS為中心再次舉辦同類會議。研討會上,瑞薩向開發(fā)者們闡述了瑞薩在華的汽車電子戰(zhàn)略,并展示了針對馬達制動、儀表板、車載音響、汽車導航等系統(tǒng)的產(chǎn)品、技術以及解決方案。作為瑞薩緊密的開發(fā)合作伙伴,EngineLab公司也展示了基于瑞薩最新的32位MCU產(chǎn)品SH-2A的引擎制動系統(tǒng)方案。 引擎和自動變速等動力系統(tǒng),是汽車的基本部件,也是中國政府和正成

- 關鍵字: 瑞薩 EngineLab MCU

SERDES的FPGA實現(xiàn)(07-100)

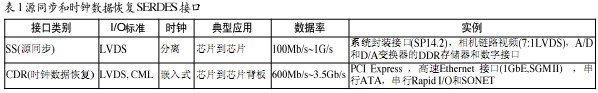

- 芯片功能的增加和數(shù)據(jù)吞吐量的要求,促使芯片行業(yè)從較低數(shù)據(jù)率的并行連接,轉向較高速度的串行連接。SERDES(Serializer-Dese rializer,)是經(jīng)高速差分對,而不是經(jīng)較低速度的并行總線傳輸串行化的數(shù)據(jù)。一個實例是用單個PCI-Express通道,替代傳統(tǒng)的32位、64MHz PCI總線(可達到2.112Gb/s),僅用4條線(運行在2.5GHz),可達到4Gb/s總數(shù)據(jù)率。簡言之,SERDES協(xié)議允許用較少的引腳數(shù)傳輸較高的數(shù)據(jù)率。

- 關鍵字: SERDES FPGA

mcu-fpga介紹

您好,目前還沒有人創(chuàng)建詞條mcu-fpga!

歡迎您創(chuàng)建該詞條,闡述對mcu-fpga的理解,并與今后在此搜索mcu-fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對mcu-fpga的理解,并與今后在此搜索mcu-fpga的朋友們分享。 創(chuàng)建詞條

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司