pll 文章 最新資訊

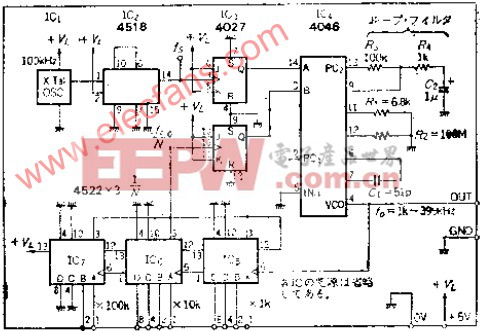

PLL-VCO設計及制作

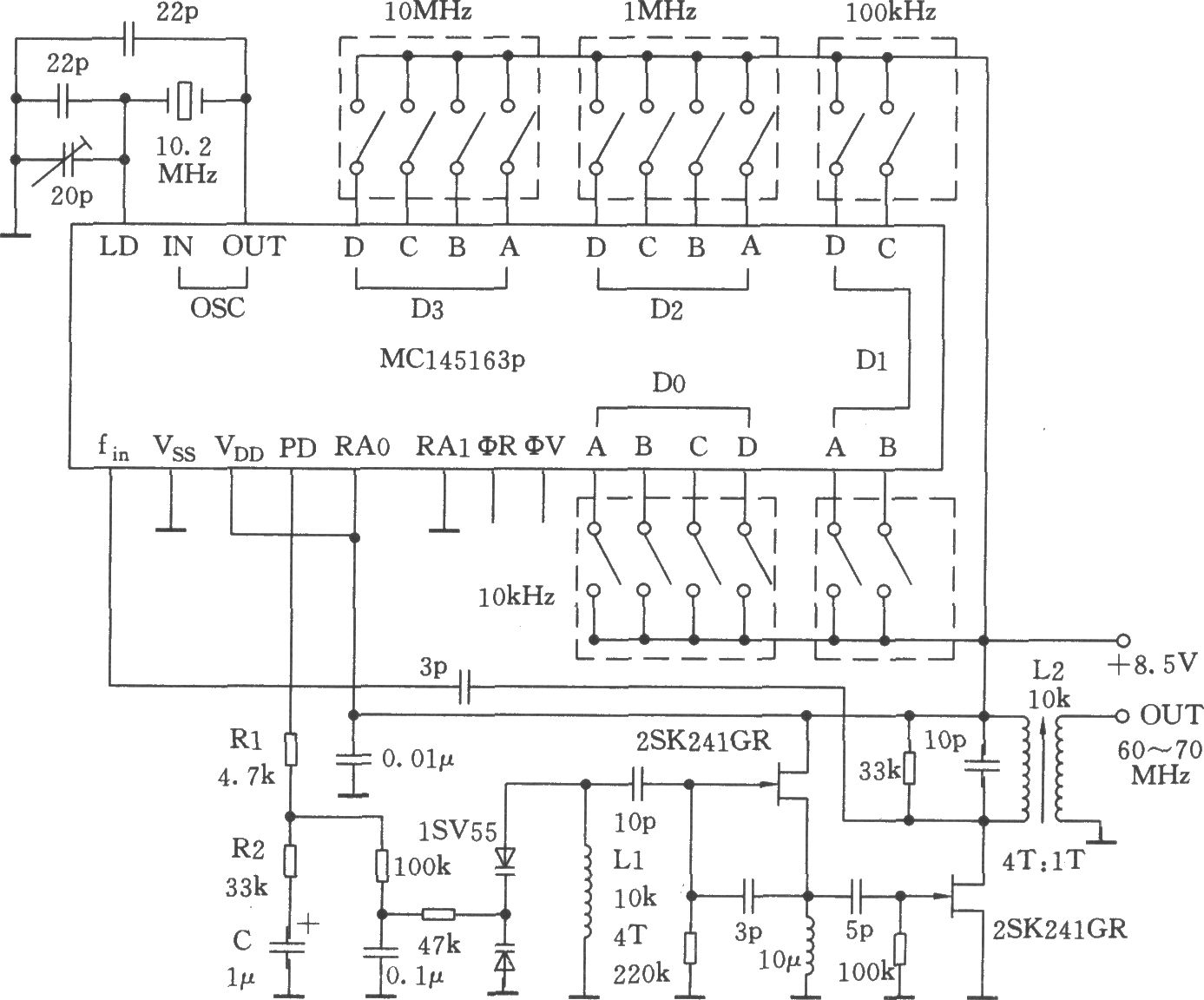

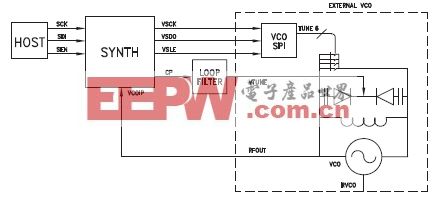

- 在此說明以晶體振蕩器做為基準振蕩器,將其與VCO以及PLL電路組合成為信號產(chǎn)生器的情形也被稱為頻率合成器。

此一PLL-VCO電路的設計規(guī)格如表l所示。振蕩頻率范圍為40M~60MHz內(nèi)的10MHz寬。每一頻率階段(step)寬幅為10 - 關鍵字: PLL-VCO

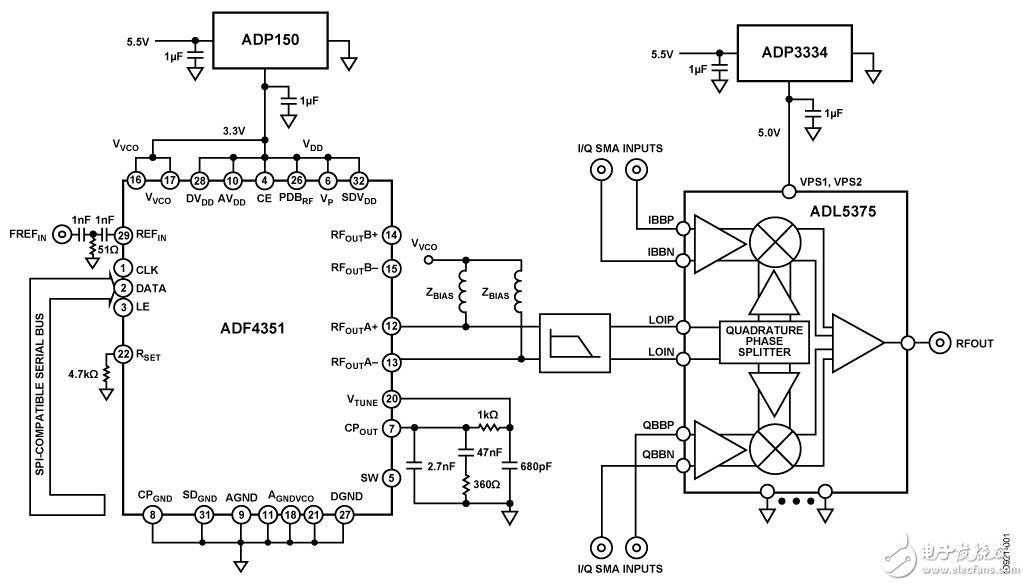

Hittite PLL以質(zhì)取勝

- 頻率源可以說是一個通信系統(tǒng)的心臟,心臟的好壞很大程度上決定著一個機體的健康狀況,而鎖相環(huán)又是頻率源的主要組成部分,因此性能優(yōu)異的鎖相環(huán)芯片對于通信系統(tǒng)來說是非常重要的。 鎖相環(huán)的相位噪聲對電子設備和電子系統(tǒng)的性能影響很大。從頻域看它分布在載波信號兩旁按冪律譜分布,無論做發(fā)射激勵信號,還是接收機本振信號以及各種頻率基準時,這些相位噪聲將在解調(diào)過程中都會和信號一樣出現(xiàn)在解調(diào)終端,引起基帶信噪比下降,誤碼率增加。 低相噪Hittite鎖相環(huán)產(chǎn)品分為集成VCO和沒有集成VCO兩種。集成VCO的PL

- 關鍵字: 世強電訊 PLL 基站類鎖相環(huán)

DSP內(nèi)嵌PLL中的CMOS壓控環(huán)形振蕩器設計

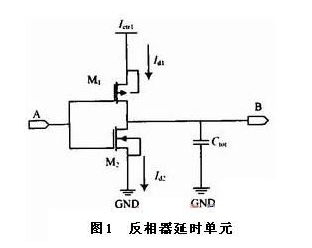

- DSP內(nèi)嵌PLL中的CMOS壓控環(huán)形振蕩器設計,本文設計了一種應用于DSP內(nèi)嵌鎖相環(huán)的低功耗、高線性CM0S壓控環(huán)形振蕩器。電路采用四級延遲單元能方便的獲得正交輸出時鐘,每級采用RS觸發(fā)結(jié)構(gòu)來產(chǎn)生差分輸出信號,在有效降低靜態(tài)功耗的同時.具有較好的抗噪聲能力。在延遲單元的設計時。綜合考慮了電壓控制的頻率范圍以及調(diào)節(jié)線性度,選擇了合適的翻轉(zhuǎn)點。 仿真結(jié)果表明.電路叮實現(xiàn)2MHz至90MHz的頻率調(diào)節(jié)范圍,在中心頻率附近具有很高的調(diào)節(jié)線性度,可完全滿足DSP芯片時鐘系統(tǒng)的要求。

- 關鍵字: 振蕩器 設計 環(huán)形 CMOS 內(nèi)嵌 PLL DSP

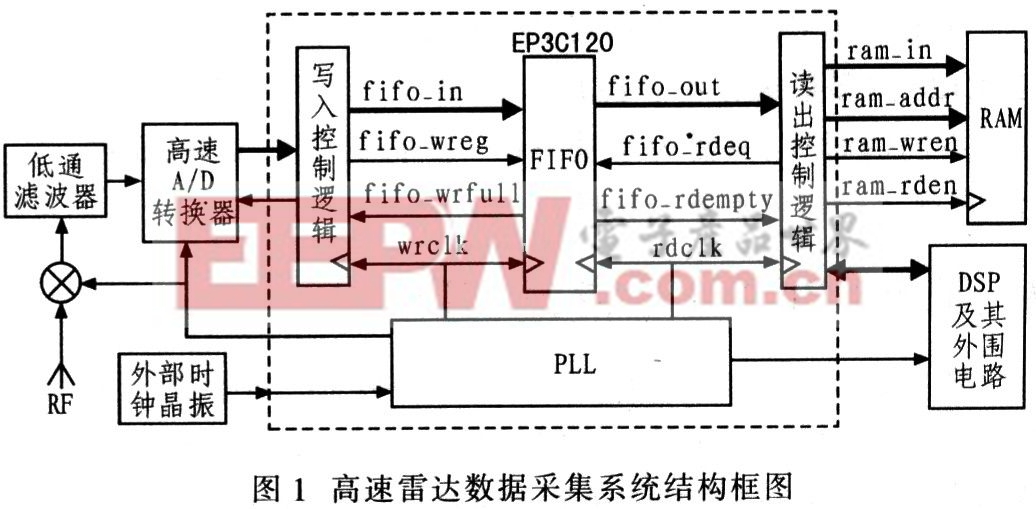

異步FIFO和PLL在高速雷達數(shù)據(jù)采集系統(tǒng)中的應用

- 異步FIFO和PLL在高速雷達數(shù)據(jù)采集系統(tǒng)中的應用,將異步FIFO和鎖相環(huán)應用到高速雷達數(shù)據(jù)采集系統(tǒng)中用來緩存A/D轉(zhuǎn)換的高速采樣數(shù)據(jù),解決嵌入式實時數(shù)據(jù)采集系統(tǒng)中,高速采集數(shù)據(jù)量大,而處理器處理速度有限的矛盾,提高系統(tǒng)的可靠性。根據(jù)FPGA內(nèi)部資源的特點,將FIFO和鎖相環(huán)設計在一塊芯片上。因為未使用外掛FIFO和PLL器件,使得板卡設計結(jié)構(gòu)簡單,并減少硬件板卡的干擾。由于鎖相環(huán)的使用,使得整個采集系統(tǒng)時鐘管理方便。異步FIFO構(gòu)成的高速緩存具有一定通用性,方便系統(tǒng)進行升級維護。

- 關鍵字: 數(shù)據(jù)采集 系統(tǒng) 應用 雷達 高速 FIFO PLL 異步

pll介紹

魔方之PLL

PLL,(Permutation of Last Layer),魔方速度還原法CFOP的最后一步,是將最后一層的方塊移動到正確位置的一步。共有21個公式。(還有其他版本)

---------------------------------------------------------------------------------------------

PLL( [ 查看詳細 ]

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司